**Features**

### **Dual 1.1Gbps Pin Electronics with Integrated** PMU and Level-Setting DACs

#### **General Description**

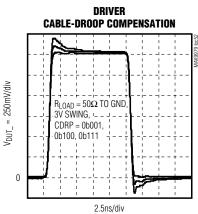

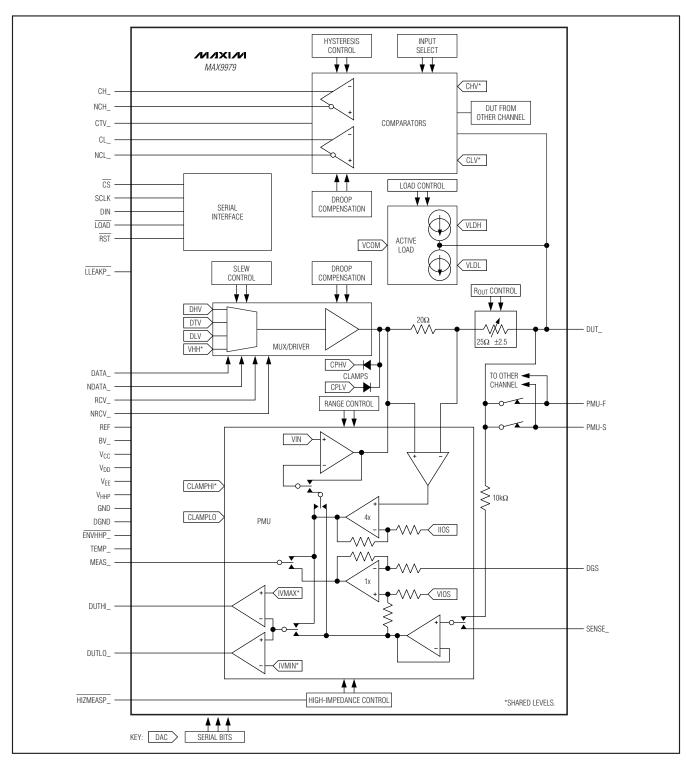

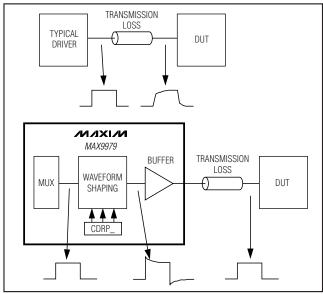

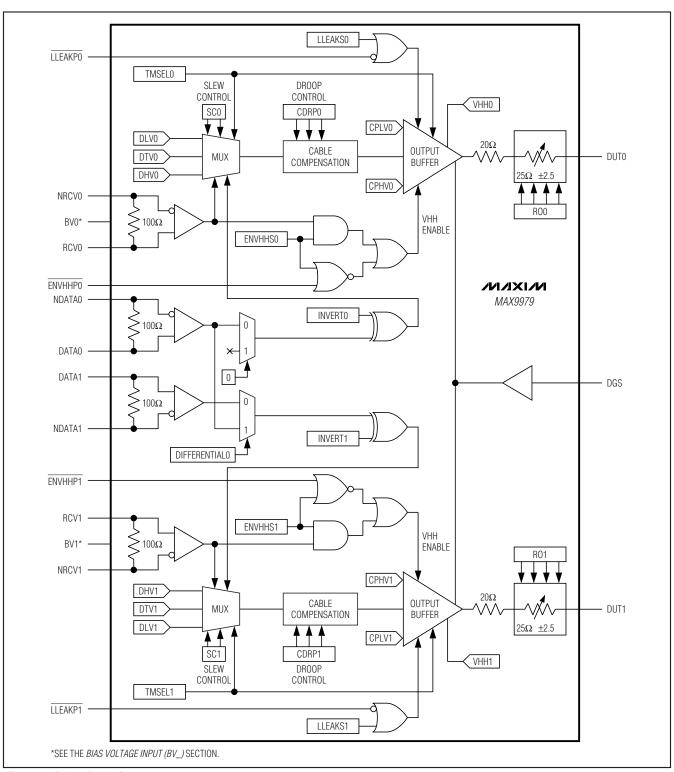

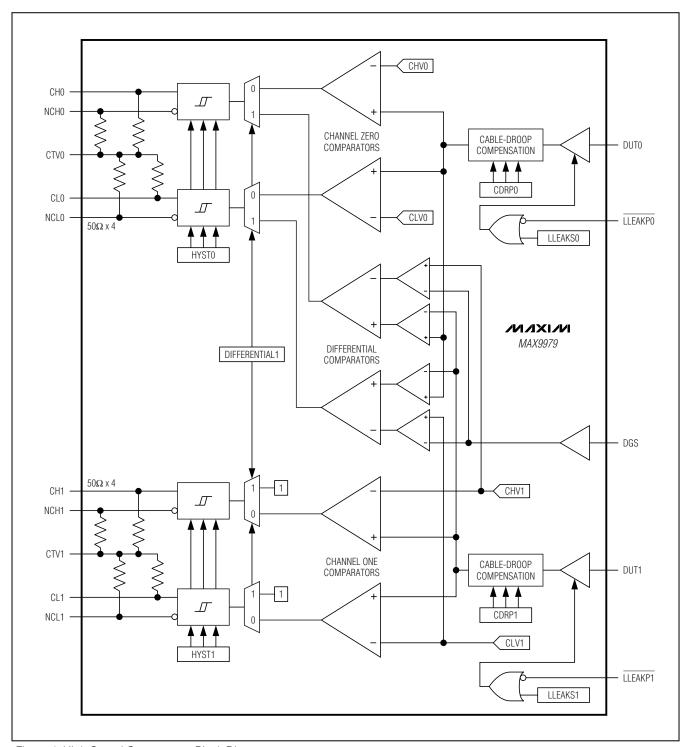

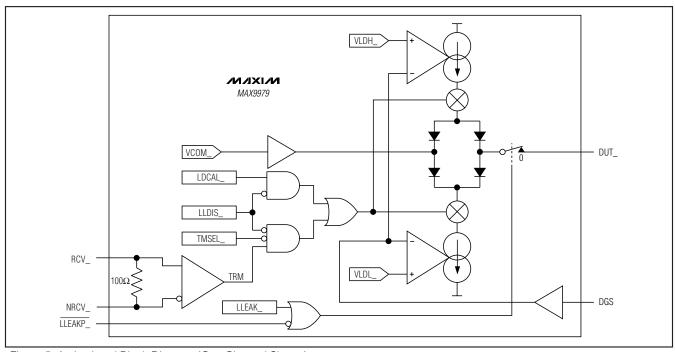

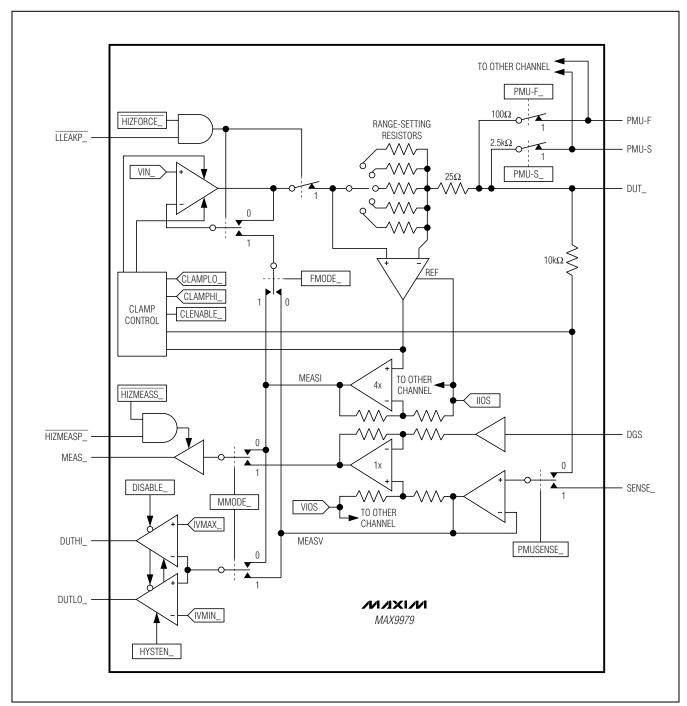

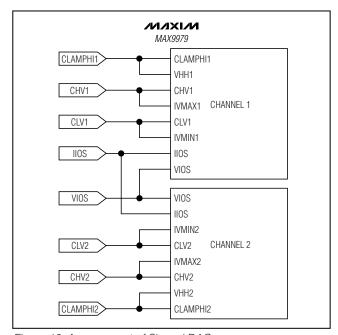

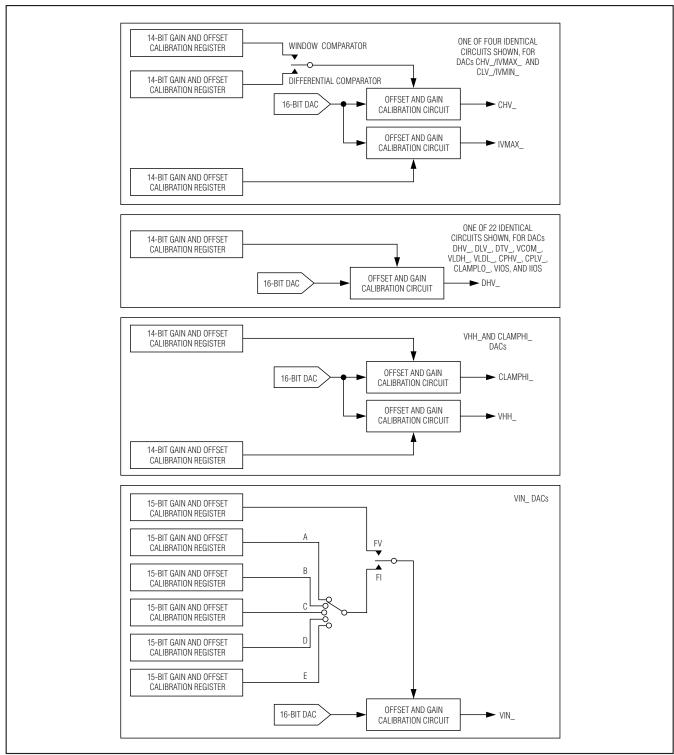

The MAX9979 fully integrated, high-performance, dualchannel pin electronics integrates multiple automatic test equipment (ATE) functions into a single IC, including driver/comparator/load (DCL), parametric measurement unit (PMU), and built-in (16-bit) level-setting digital-to-analog converters (DACs). The device is ideal for memory and SOC tester applications. Each channel includes a fourlevel pin driver, window comparator, differential comparator, dynamic clamps, a versatile PMU, an active load, a high-voltage (VHH) programmable level, and 14 independent level-setting DACs. The MAX9979 features programmable cable-droop compensation for the driver output and for the comparator input, adjustable driver output resistance that allows optimal performance over typical data-path transmission-line variations, slew-rate adjustment, and a programmable high-voltage driver output.

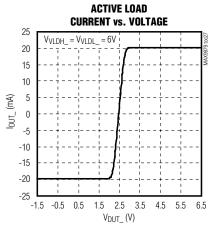

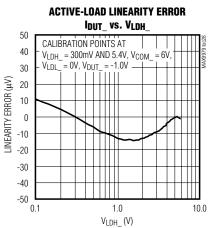

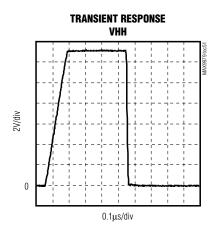

The MAX9979 driver features a wide 8V (-1.5V to +6.5V) high-speed operating voltage range and a VHH programmable range of up to +13V. Operation modes include high-impedance, active-termination (3rd-level drive) and VHH (4th-level drive) modes. The device is highly linear even at low voltage swings. The driver provides highspeed differential control inputs compatible with most high-speed logic families. The window comparators provide extremely low timing variation over changes in slew rate, pulse width, and overdrive voltage. In high-impedance mode, the MAX9979 features dynamic clamps that dampen high-speed device-under-test (DUT) waveforms. The 20mA active load facilitates fast contact testing when used in conjunction with the comparators, and functions as a pullup/pulldown for open-drain/collector DUT outputs. The PMU offers five current ranges from ±2µA to ±50mA and can force and measure current or voltage. An SPI™-compatible serial interface configures the MAX9979.

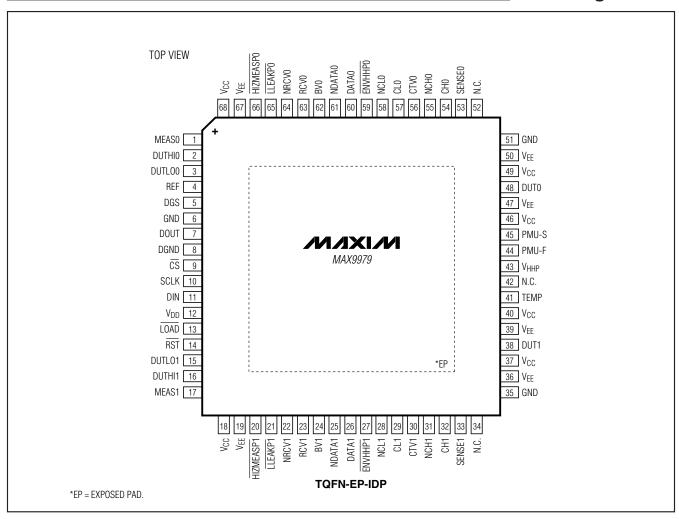

The MAX9979 is available in a small footprint, 68-pin (10mm x 10mm x 1mm) TQFN-EP-IDP package with exposed pad on the top for easy heat removal. Power dissipation is 1.2W per channel (typ) over the full operating voltage range with the active load disabled. The MAX9979 operates over an internal die temperature range of +40°C to +100°C and provides a temperature monitor output.

**Applications**

Memory ATE Testers SOC ATE Testers

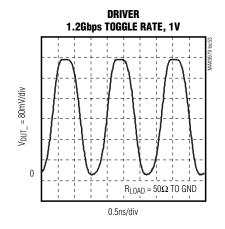

♦ High Speed: 1.1Gbps at 1Vp-p

♦ Extremely Low Power Dissipation: 1.2W/Channel (Active Load Disabled)

♦ Wide Voltage Range: -1.5V to +6.5V and Up to 13V VHH

♦ Wide Voltage Swing Range: 50mVp-p to 13Vp-p

♦ Low-Leak Mode: 10nA max

♦ Integrated Termination-on-the-Fly (3rd-Level Drive)

♦ Integrated VHH High Voltage (4th-Level Drive)

♦ Integrated Voltage Clamps

♦ Integrated 20mA Active Load

♦ Integrated Per-Pin PMU

♦ Integrated Level-Setting CALDACs

**♦** Programmable Cable-Droop Compensation for **Both Driver Output and Comparator Input**

**♦ Programmable Driver Output Impedance**

**♦** Four Slew-Rate Settings for Driver Output

♦ Analog Measure Bus

♦ Very Low Timing Dispersion

♦ Minimal External Component Count

**♦ SPI-Compatible Serial Control Interface**

♦ 68-Pin Thermally Enhanced TQFN Package with **Top-Side Heat Removal**

### **Ordering Information**

| PART         | TEMP RANGE   | PIN-PACKAGE     |

|--------------|--------------|-----------------|

| MAX9979KCTK+ | 0°C to +70°C | 68 TQFN-EP-IDP* |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

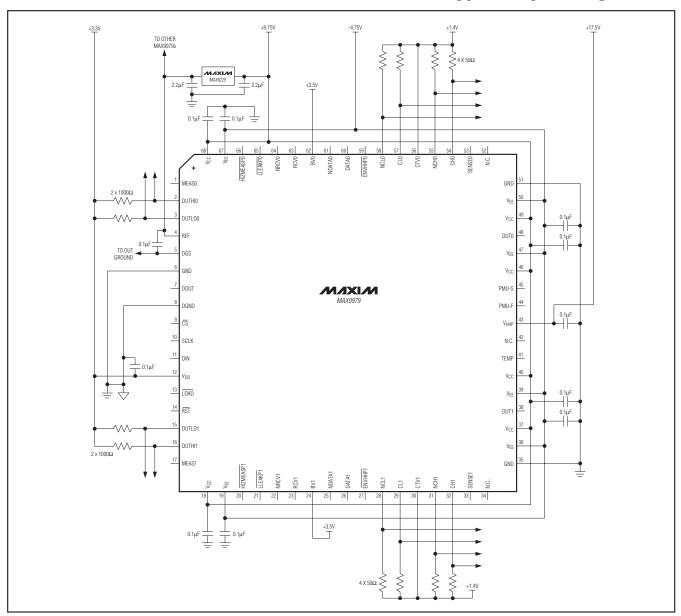

Pin Configuration and Typical Operating Circuit appear at end of data sheet.

SPI is a trademark of Motorola, Inc.

<sup>\*</sup>EP-IDP = Exposed pad, inverted die pad.

#### **ABSOLUTE MAXIMUM RATINGS**

| VCC to GND       -0.3V to +11V         VEE to GND       -5.5V to +0.3V         VCC to VEE       -0.3V to +16.5V         VDD to DGND       -0.3V to +5.2V                                  | TEMP to GND                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>HHP</sub> to GND                                                                                                                                                                   | Current into LLEAKP_, HIZMEASP_, ENVHHP_, DUTHI_, DUTLO±30mA                                                                                                    |

| CTV_, BV_ to GND0.3V to +5V                                                                                                                                                               | PMU-F Continuous Current±35mA                                                                                                                                   |

| DATA_, NDATA_, RCV_,<br>NRCV_ to GND(V <sub>EE</sub> - 0.3V) to (V <sub>BV</sub> _ + 0.3V)                                                                                                | PMU-F Peak Current±70mA<br>PMU-S Continuous Current±1mA                                                                                                         |

| CH_, NCH_, CL_, NCL_ to GND1.5V to (VCTV_ + 0.3V)  Current into CH_, NCH_, CL_, NCL                                                                                                       | PMU-S Peak Current±20mA<br>DGS to GND±0.3V                                                                                                                      |

| DATA_ to NDATA_, RCV_ to NRCV±1V DUT_, PMU-F, PMU-S, SENSE_ to GND (non-VHH mode)(VFF - 0.3V) to (VCC + 0.3V)                                                                             | DUT_, SENSE_ Short-Circuit  Duration to $V_{CC}$ , $V_{EE}$                                                                                                     |

| DUT_, PMU-F, PMU-S, SENSE_ to GND (VHH mode)3.5V to +13.5V  SCLK, DIN, CS, RST, LOAD to GND0.3V to (VDD + 0.3V)  LLEAKP_, HIZMEASP_, ENVHHP_, DUTHI_,  DUTLO_, to GND0.3V to (VDD + 0.3V) | MAX9979KCTK (derate 125mW/°C above +70°C)10W Storage Temperature Range65°C to +150°C Maximum Junction Temperature+150°C Lead Temperature (soldering, 10s)+300°C |

<sup>\*</sup>Dissipation wattage values are based on still air with no heatsink. Actual maximum power dissipation is a function of heat extraction technique and may be substantially higher.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### PACKAGE THERMAL CHARACTERISTICS\*\*

**TQFN**

Junction-to-Case Thermal Resistance (θJA).....8.0°C/W Junction-to-Ambient Thermal Resistance (θJC)......0.3°C/W

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 9.75 \text{V}, V_{EE} = -4.75 \text{V}, V_{DD} = 3.3 \text{V}, V_{HHP} = 17.5 \text{V}, V_{DHV} = 3 \text{V}, V_{DLV} = 0 \text{V}, V_{DTV} = 1.5 \text{V}, \text{SC1} = \text{SC0} = 0 \text{V}, V_{CPHV} = 7.2 \text{V}, V_{CPLV} = -2.2 \text{V}, V_{CTV} = 1.4 \text{V}, V_{BV} = 4 \text{V}, V_{DGS} = V_{GND} = 0 \text{V}, V_{CHV} = V_{IVMAX} = 2 \text{V}, V_{CLV} = V_{IVMIN} = 1 \text{V}, V_{CDM} = 2.5 \text{V}, V_{LDHV} = 0 \text{V}, V_{LDLV} = 0 \text{V}, V_{ID} = 2.5 \text{V}, V_{IDS} = 0 \text{V}, V_{IDS} = 2.5 \text{V}, V_{CLMPH} = 5 \text{V}, V_{CLMPLO} = 0 \text{V}, V_{HH} = 10 \text{V}, CDRP = 0 \text{b001}, RO = 0 \text{b1000}, HYST = 0 \text{b000}, Z_{LOAD} = 50\Omega, T_{J} = +70^{\circ}\text{C} \text{ to an accuracy of } \pm 15^{\circ}\text{C}, \text{ unless otherwise noted}. \text{ All temperature coefficients are measured at } T_{J} = +40^{\circ}\text{C} \text{ to } +100^{\circ}\text{C}, \text{ unless otherwise noted}.) \text{ (Note 1)}$

| PARAMETER                                              | SYMBOL                          | CONDITIONS                                                                    | MIN            | TYP        | MAX   | UNITS |

|--------------------------------------------------------|---------------------------------|-------------------------------------------------------------------------------|----------------|------------|-------|-------|

| DRIVER                                                 |                                 |                                                                               |                |            |       |       |

| DC CHARACTERISTICS ( $R_L \ge 10$                      | M $\Omega$ , unless $\mathbf c$ | therwise noted; includes DAC error)                                           |                |            |       |       |

|                                                        | $V_{DHV}$                       | V <sub>DLV</sub> _ = -1.5V, V <sub>DTV</sub> _ = 1.5V                         | -1             | .45 to +6. | .50   |       |

| Output-Voltage Range                                   | $V_{DLV}$                       | V <sub>DHV</sub> _ = 6.5V, V <sub>DTV</sub> _ = 1.5V                          | -1.50 to +6.45 |            |       | V     |

|                                                        | $V_{DTV}$                       | V <sub>DHV</sub> = 6.5V, V <sub>DLV</sub> = -1.5V (Note 2)                    | -1.50          |            | +6.50 |       |

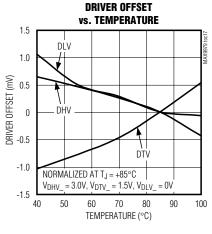

|                                                        | $V_{DHV}$                       | V <sub>DHV</sub> = 3V, V <sub>DLV</sub> = -1.5V, V <sub>DTV</sub> = 1.5V      |                |            | ±5    |       |

| Output Offset Voltage                                  | $V_{DLV}$                       | V <sub>DLV</sub> _ = 0V, V <sub>DHV</sub> _ = 6.5V, V <sub>DTV</sub> _ = 1.5V |                |            | ±5    | mV    |

|                                                        | V <sub>DTV</sub>                | $V_{DTV} = 1.5V, V_{DHV} = 6.5V, V_{DLV} = -1.5V$                             |                |            | ±5    |       |

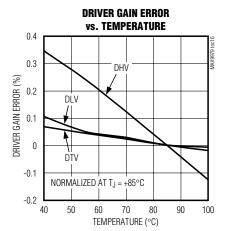

| Output-Voltage Temperature<br>Coefficient (Notes 3, 4) |                                 | DHV_, DLV_, DTV_                                                              |                | ±75        | ±500  | μV/°C |

<sup>\*\*</sup>Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

#### **ELECTRICAL CHARACTERISTICS (continued)**

$\begin{array}{l} (V_{CC}=9.75\text{V},\ V_{EE}=\text{-}4.75\text{V},\ V_{DD}=3.3\text{V},\ V_{DHP}=17.5\text{V},\ V_{DHV}=3\text{V},\ V_{DLV}=\text{0V},\ V_{DTV}=1.5\text{V},\ SC1=SC0=\text{0V},\ V_{CPHV}=7.2\text{V},\ V_{CPLV}=\text{-}2.2\text{V},\ V_{CTV}=1.4\text{V},\ V_{BV}=4\text{V},\ V_{DGS}=V_{GND}=0\text{V},\ V_{CHV}=V_{IVMAX}=2\text{V},\ V_{CLV}=V_{IVMIN}=1\text{V},\ V_{COM}=2.5\text{V},\ V_{LDHV}=0\text{V},\ V_{LDLV}=0\text{V},\ V_{ID}=2.5\text{V},\ V_{VIOS}=0\text{V},\ V_{IDS}=2.5\text{V},\ V_{CLAMPHI}=5\text{V},\ V_{CLAMPLO}=0\text{V},\ V_{HH}=10\text{V},\ CDRP=0\text{bb001},\ RO=0\text{b1000},\ HYST=0\text{b000},\ Z_{LOAD}=50\Omega,\ T_{J}=+70^{\circ}\text{C}\ to\ an\ accuracy\ of\ \pm15^{\circ}\text{C},\ unless\ otherwise\ noted.\ All\ temperature\ coefficients\ are\ measured\ at\ T_{J}=+40^{\circ}\text{C}\ to\ +100^{\circ}\text{C},\ unless\ otherwise\ noted.) \label{eq:coefficients}$

| PARAMETER       | SYMBOL           | CON                                                                                                                                                                             | IDITIONS                                                                                                     | MIN   | TYP  | MAX   | UNITS |

|-----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

|                 |                  |                                                                                                                                                                                 | $V_{DLV\_}$ = -1.5V, $V_{DTV\_}$ = 1.5V, $V_{DHV\_}$ = 0V and 4.5V                                           |       | 1    | 1.002 |       |

| Gain            | A <sub>DLV</sub> | $V_{DHV}$ = 6.5V, $V_{DTV}$ and 4.5V                                                                                                                                            | _ = 1.5V, V <sub>DLV</sub> _ = 0V                                                                            | 0.998 | 1    | 1.002 | V/V   |

|                 | A <sub>DTV</sub> | V <sub>DHV</sub> _ = 6.5V, V <sub>DLV</sub> _ = -1.5V, V <sub>DTV</sub> _ = 0V and 4.5V                                                                                         |                                                                                                              | 0.998 | 1    | 1.002 |       |

|                 |                  |                                                                                                                                                                                 | V <sub>DLV</sub> _ = -1.5V, V <sub>DTV</sub> _<br>= 1.5V, V <sub>DHV</sub> _ = 0V,<br>0.75V, 1.5V, 2.25V, 3V |       |      | ±2    |       |

|                 |                  | 0 to 3V relative to calibration points at 0 and 3V                                                                                                                              | V <sub>DHV</sub> _ = 6.5V, V <sub>DTV</sub> _ = 1.5V, V <sub>DLV</sub> _ = 0V, 0.75V, 1.5V, 2.25V, 3V        |       |      | ±2    |       |

|                 |                  |                                                                                                                                                                                 | V <sub>DLV</sub> _ = -1.5V, V <sub>DHV</sub> _<br>= 6.5V, V <sub>DTV</sub> _ = 0V,<br>0.75V, 1.5V, 2.25V, 3V |       |      | ±2    |       |

|                 |                  |                                                                                                                                                                                 | V <sub>DLV</sub> _ = -1.5V, V <sub>DTV</sub> _<br>= 1.5V, V <sub>DHV</sub> _ = -1V<br>and 6V                 |       |      | ±4.5  |       |

| Linearity Error |                  | -1V to 6V relative to calibration points at 0 and 3V $V_{DHV\_} = 6.5V, V_{DTV\_} = 1.5V, V_{DLV\_} = -1V$ and 6V $V_{DLV\_} = -1.5V, V_{DHV\_} = 6.5V, V_{DTV\_} = -1V$ and 6V | $1.5V, V_{DLV} = -1V$                                                                                        |       |      | ±4.5  | mV    |

|                 |                  |                                                                                                                                                                                 |                                                                                                              |       | ±4.5 |       |       |

|                 |                  |                                                                                                                                                                                 | V <sub>DLV</sub> _ = -1.5V, V <sub>DTV</sub> _<br>= 1.5V, V <sub>DHV</sub> _ =<br>-1.25V and 6.5V            |       |      | ±6    |       |

|                 |                  | Full range relative<br>to calibration<br>points at 0 and 3V                                                                                                                     | V <sub>DHV</sub> = 6.5V, V <sub>DTV</sub> = 1.5V, V <sub>DLV</sub> = -1.5V and 6.25V                         |       |      | ±6    |       |

|                 |                  |                                                                                                                                                                                 | V <sub>DLV</sub> _ = -1.5V, V <sub>DHV</sub> _<br>= 6.5V, V <sub>DTV</sub> _ = -1.5V<br>and 6.5V             |       |      | ±6    |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$\begin{array}{l} (V_{CC}=9.75\text{V},\ V_{EE}=\text{-}4.75\text{V},\ V_{DD}=3.3\text{V},\ V_{DHP}=17.5\text{V},\ V_{DHV}=3\text{V},\ V_{DLV}=\text{0V},\ V_{DTV}=1.5\text{V},\ SC1=SC0=\text{0V},\ V_{CPHV}=7.2\text{V},\ V_{CPLV}=\text{-}2.2\text{V},\ V_{CTV}=1.4\text{V},\ V_{BV}=4\text{V},\ V_{DGS}=V_{GND}=\text{0V},\ V_{CHV}=V_{IVMAX}=2\text{V},\ V_{CLV}=V_{IVMIN}=1\text{V},\ V_{COM}=2.5\text{V},\ V_{LDHV}=0\text{V},\ V_{LDLV}=0\text{V},\ V_{ID}=2.5\text{V},\ V_{IOS}=0\text{V},\ V_{IOS}=2.5\text{V},\ V_{CLAMPH}=5\text{V},\ V_{CLAMPLO}=0\text{V},\ V_{HH}=10\text{V},\ CDRP=0\text{b001},\ RO=0\text{b1000},\ HYST=0\text{b000},\ Z_{LOAD}=50\Omega,\ T_{J}=+70^{\circ}\text{C}\ to\ an\ accuracy\ of\ \pm15^{\circ}\text{C},\ unless\ otherwise\ noted.\ All\ temperature\ coefficients\ are\ measured\ at\ T_{J}=+40^{\circ}\text{C}\ to\ +100^{\circ}\text{C},\ unless\ otherwise\ noted.) \ (Note\ 1) \end{array}$

| PARAMETER                             | SYMBOL | CON                                                                                                                                   | IDITIONS                                                                                     | MIN  | TYP  | MAX  | UNITS |  |

|---------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|------|------|-------|--|

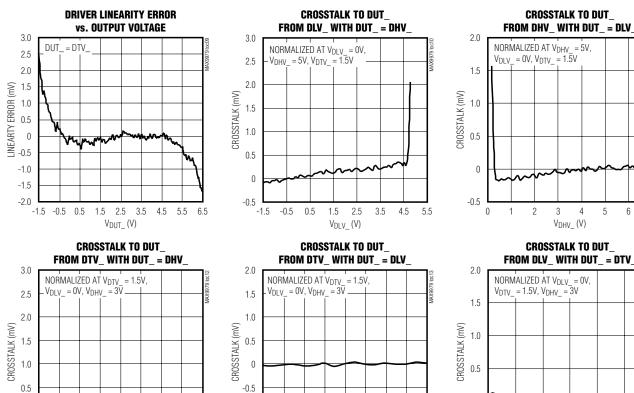

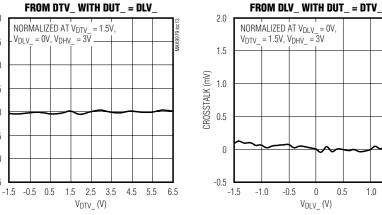

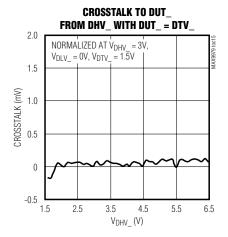

|                                       |        | DHV_ to DLV_                                                                                                                          | V <sub>DLV</sub> _ = 0V, V <sub>DTV</sub> _ = 1.5V, V <sub>DHV</sub> _ = 0.2V and 6.5V       |      |      | ±7   |       |  |

| Crosstalk                             |        | DLV_ to DHV_                                                                                                                          | V <sub>DHV</sub> _ = 5V, V <sub>DTV</sub> _ = 1.5V, V <sub>DLV</sub> _ = -1.5 and 4.8V       |      |      | ±7   |       |  |

|                                       |        | DTV_ to DLV_ and DHV_                                                                                                                 | V <sub>DHV</sub> _ = 3V, V <sub>DLV</sub> _ = 0V, V <sub>DTV</sub> _ = -1.5V and 6.5V        |      |      | ±2   | mV    |  |

|                                       |        | DHV_ to DTV_                                                                                                                          | V <sub>DTV</sub> _ = 1.5V, V <sub>DLV</sub> _ = 0V, V <sub>DHV</sub> _ = 1.6V and 3V         |      |      | ±3   |       |  |

|                                       |        | DLV_ to DTV_                                                                                                                          | V <sub>DTV</sub> _ = 1.5V, V <sub>DHV</sub> _ = 3V, V <sub>DLV</sub> _ = 0 and 1.4V          |      |      | ±3   |       |  |

| Term Voltage                          |        | Dependence on DATA_                                                                                                                   | V <sub>DTV</sub> _ = 1.5V, V <sub>DHV</sub> _ = 3V, V <sub>DLV</sub> _ = 0V, DATA_ = 0 and 1 |      |      | ±2   | mV    |  |

| DO Davis Overalis Dairatias           |        | DHV_                                                                                                                                  | V <sub>DHV</sub> _ = 3V                                                                      | 40   |      |      |       |  |

| DC Power-Supply Rejection (Note 5)    |        | DLV_                                                                                                                                  | $V_{DLV} = 0V$                                                                               | 40   |      |      | dB    |  |

| · · · · · · · · · · · · · · · · · · · |        | DTV_                                                                                                                                  | $V_{DTV} = 1.5V$                                                                             | 40   |      |      |       |  |

| DC Drive Current Limit                |        | V <sub>DHV</sub> _ = 6.5V,                                                                                                            | DATA_ = 1, V <sub>DUT_</sub> = -1.5V                                                         | +60  |      | +110 | - mA  |  |

| Do Drive Garretti Limit               |        | V <sub>DLV</sub> = -1.5V                                                                                                              | DATA_ = 0, V <sub>DUT_</sub> = 6.5V                                                          | -110 |      | -60  | IIIA  |  |

| DC Output Resistance                  |        | (Note 6)                                                                                                                              |                                                                                              | 48   | 50   | 52   | Ω     |  |

| DC Output Resistance Variation        |        | DATA_ = 1, V <sub>DHV</sub> _ = 1.5V, I <sub>DUT</sub> _ = 1mA, 8                                                                     |                                                                                              | 1    | 2    |      |       |  |

| (Note 7)                              |        | DATA_ = 0, V <sub>DHV</sub> _ = 3V, V <sub>DLV</sub> _ = 0V, V <sub>DTV</sub> _ = 1.5V, I <sub>DUT</sub> _ = -1mA, -8mA, -15mA, -40mA |                                                                                              |      | 1    | 2    | Ω     |  |

| Adjustable Output Resistance<br>Range |        | $R_O = 0xF \text{ vs. } R_O = 0$<br>$R_O = 0x8, \text{ resolution}$                                                                   | $0x8$ and $R_O = 0x0$ vs.<br>n of 0.36 $\Omega$ (Note 6)                                     |      | ±2.5 |      | Ω     |  |

NIXIN

#### **ELECTRICAL CHARACTERISTICS (continued)**

$\begin{array}{l} (V_{CC}=9.75\text{V},\ V_{EE}=\text{-}4.75\text{V},\ V_{DD}=3.3\text{V},\ V_{DHP}=17.5\text{V},\ V_{DHV}=3\text{V},\ V_{DLV}=\text{0V},\ V_{DTV}=1.5\text{V},\ SC1=\text{SC0}=\text{0V},\ V_{CPHV}=7.2\text{V},\ V_{CPLV}=\text{-}2.2\text{V},\ V_{CTV}=1.4\text{V},\ V_{BV}=4\text{V},\ V_{DGS}=\text{V}_{GND}=\text{0V},\ V_{CHV}=\text{V}_{IVMAX}=2\text{V},\ V_{CLV}=\text{V}_{IVMIN}=1\text{V},\ V_{COM}=2.5\text{V},\ V_{LDHV}=0\text{V},\ V_{LDLV}=0\text{V},\ V_{ID}=2.5\text{V},\ V_{VIOS}=0\text{V},\ V_{IOS}=2.5\text{V},\ V_{CLAMPHI}=5\text{V},\ V_{CLAMPLO}=0\text{V},\ V_{HH}=10\text{V},\ CDRP=0\text{b001},\ RO=0\text{b1000},\ HYST=0\text{b000},\ Z_{LOAD}=50\Omega,\ T_{J}=+70^{\circ}\text{C}\ \text{to\ an\ accuracy\ of\ }\pm15^{\circ}\text{C},\ \text{unless\ otherwise\ noted}.\ \text{All\ temperature\ coefficients\ are\ measured\ at\ }T_{J}=+40^{\circ}\text{C}\ \text{to\ }+100^{\circ}\text{C},\ \text{unless\ otherwise\ noted}.\ \end{array}$

| PARAMETER                          | SYMBOL               | CONDITIONS                                                                                                          | MIN | TYP  | MAX | UNITS |

|------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

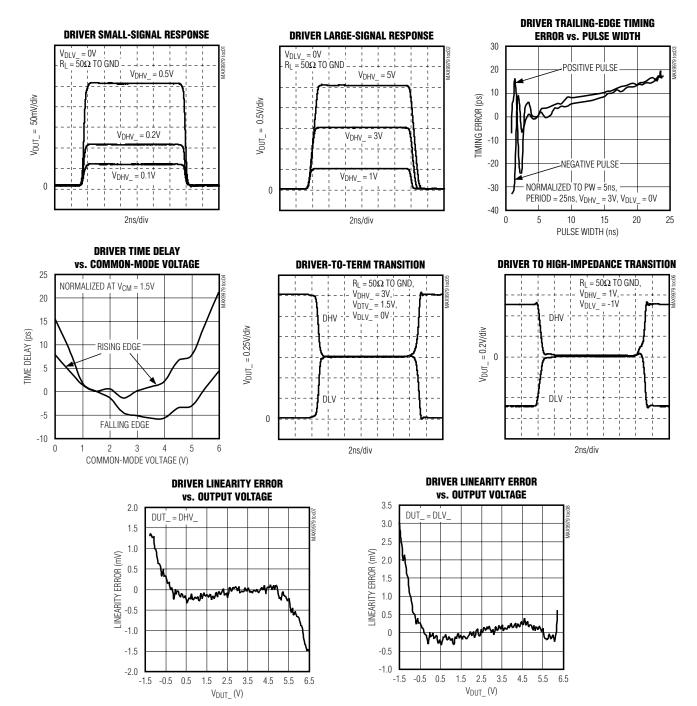

| AC CHARACTERISTICS (RDUT_          | = <b>50</b> Ω to Gro | und) (Note 8)                                                                                                       |     |      |     | •     |

| Dynamic Drive Current              |                      | (Note 9)                                                                                                            |     | ±130 |     | mA    |

|                                    |                      | Cable-droop compensation off, $V_{DLV} = 0V$ , $V_{DHV} = 0.1V$                                                     |     | 30   |     |       |

| Drive-Mode Overshoot               |                      | Cable-droop compensation off, $V_{DLV} = 0V$ , $V_{DHV} = 1V$                                                       |     | 40   |     | m\/   |

|                                    |                      | Cable-droop compensation off, $V_{DLV} = 0V$ , $V_{DHV} = 3V$                                                       |     | 50   |     | mV    |

|                                    |                      | Cable-droop compensation off, $V_{DLV} = 0V$ , $V_{DHV} = 5V$                                                       |     | 50   |     |       |

| Cable-Droop Compensation           |                      | V <sub>DLV</sub> _ = 0V, V <sub>DHV</sub> _ = 3V, CDRP_ = 0b000                                                     |     | 0    |     | %     |

|                                    |                      | V <sub>DLV</sub> _ = 0V, V <sub>DHV</sub> _ = 3V, CDRP_ = 0b111                                                     |     | 10   |     | /0    |

| Termination-Mode Overshoot         |                      | Cable-droop compensation off (Note 10)                                                                              |     | 0    |     | mV    |

|                                    |                      | To within 100mV, $V_{DHV} = 5V$ , $V_{DLV} = 0V$                                                                    |     | 0.25 | 1   |       |

| Settling Time (Notes 4, 11)        |                      | To within 50mV, $V_{DHV} = 3V$ , $V_{DLV} = 0V$                                                                     |     | 0.25 | 1   | ns    |

|                                    |                      | To within 50mV, $V_{DHV} = 0.5V$ , $V_{DLV} = 0V$                                                                   |     | 0.25 | 1   |       |

| TIMING CHARACTERISTICS (No         | tes 8, 12)           |                                                                                                                     |     |      |     |       |

|                                    |                      | Data to output, V <sub>DHV</sub> = 3V, V <sub>DLV</sub> = 0V (Note 13)                                              | 1   | 1.9  | 4   |       |

| Description Delay                  |                      | Drive to term, term to drive (Notes 4, 14)                                                                          | 1.7 | 2.7  | 3.7 | 1     |

| Propagation Delay                  |                      | Drive to high impedance, high impedance to drive, V <sub>DHV</sub> = 1V, V <sub>DLV</sub> = -1V (Notes 4, 15)       | 1.4 | 2.4  | 3.4 | ns    |

|                                    |                      | t <sub>LH</sub> vs. t <sub>HL</sub> (Note 4)                                                                        |     | ±40  | ±80 |       |

|                                    |                      | Drivers within package, same edge                                                                                   |     | ±40  |     | ps    |

| Propagation-Delay Match            |                      | Drive to high impedance vs. high impedance to drive, V <sub>DHV</sub> = 1V, V <sub>DLV</sub> = -1V (Note 16)        |     | ±0.5 |     |       |

|                                    |                      | High impedance vs. data                                                                                             |     | ±0.5 |     | ns    |

|                                    |                      | Drive to term vs. term to drive, V <sub>DHV</sub> = 3V, V <sub>DLV</sub> = 0V, V <sub>DTV</sub> = 1.5V (Note 17)    |     | ±0.3 |     |       |

|                                    |                      | Terminate vs. data                                                                                                  |     | ±0.8 |     |       |

| Propagation-Delay Channel<br>Match |                      | Differential mode, V <sub>DHV</sub> = 1V, V <sub>DLV</sub> = 0V, channel 1 inverted, DIFFERENTIAL0 = 1, INVERT1 = 1 |     | ±40  |     | ps    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$\begin{array}{l} (V_{CC}=9.75\text{V},\ V_{EE}=\text{-}4.75\text{V},\ V_{DD}=3.3\text{V},\ V_{DHP}=17.5\text{V},\ V_{DHV}=3\text{V},\ V_{DLV}=\text{0V},\ V_{DTV}=1.5\text{V},\ SC1=SC0=\text{0V},\ V_{CPHV}=7.2\text{V},\ V_{CPLV}=\text{-}2.2\text{V},\ V_{CTV}=1.4\text{V},\ V_{BV}=4\text{V},\ V_{DGS}=V_{GND}=\text{0V},\ V_{CHV}=V_{IVMAX}=2\text{V},\ V_{CLV}=V_{IVMIN}=1\text{V},\ V_{COM}=2.5\text{V},\ V_{LDHV}=0\text{V},\ V_{LDLV}=0\text{V},\ V_{ID}=2.5\text{V},\ V_{IOS}=0\text{V},\ V_{IOS}=2.5\text{V},\ V_{CLAMPH}=5\text{V},\ V_{CLAMPLO}=0\text{V},\ V_{HH}=10\text{V},\ CDRP=0\text{b001},\ RO=0\text{b1000},\ HYST=0\text{b000},\ Z_{LOAD}=50\Omega,\ T_{J}=+70^{\circ}\text{C}\ to\ an\ accuracy\ of\ \pm15^{\circ}\text{C},\ unless\ otherwise\ noted.\ All\ temperature\ coefficients\ are\ measured\ at\ T_{J}=+40^{\circ}\text{C}\ to\ +100^{\circ}\text{C},\ unless\ otherwise\ noted.) \ (Note\ 1) \end{array}$

| PARAMETER                                    | SYMBOL | СО                                                                                                                                                                                         | NDITIONS                                                                       | MIN | TYP  | MAX  | UNITS |

|----------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----|------|------|-------|

| Propagation-Delay Temperature<br>Coefficient |        | V <sub>DHV</sub> _ = 3V, V <sub>DLV</sub> _                                                                                                                                                | V <sub>DHV</sub> _ = 3V, V <sub>DLV</sub> _ = 0V (Note 4)                      |     | 3    | 5    | ps/°C |

|                                              |        |                                                                                                                                                                                            | V <sub>DHV</sub> = 1V, V <sub>DLV</sub> = 0V, 1ns to 24ns pulse width (Note 4) |     | ±25  | ±60  |       |

| Propagation-Delay Change                     |        | Change vs. pulse width (Note 18)                                                                                                                                                           | V <sub>DHV</sub> = 3V, V <sub>DLV</sub> = 0V, 1ns to 24ns pulse width (Note 4) |     | ±35  | ±60  |       |

|                                              |        |                                                                                                                                                                                            | V <sub>DHV</sub> = 5V, V <sub>DLV</sub> = 0V, 1.5ns to 23.5ns pulse width      |     | ±100 |      | ps    |

|                                              |        | Peak-to-peak change vs. common mode, V <sub>DHV_</sub> - V <sub>DLV_</sub> = 1V, V <sub>DHV_</sub> = 0 to 6V, using a DC-blocking capacitor (Note 4)                                       |                                                                                |     | 50   | 60   |       |

|                                              |        | 0.2V <sub>P-P</sub> programmed, V <sub>DHV</sub> = 0.2V,<br>V <sub>DLV</sub> = 0V, 20% to 80%<br>1V <sub>P-P</sub> programmed, V <sub>DHV</sub> = 1V,<br>V <sub>DLV</sub> = 0V, 10% to 90% |                                                                                |     | 275  |      |       |

| Diag and Fall Time                           |        |                                                                                                                                                                                            |                                                                                | 330 | 450  | 550  |       |

| Rise-and-Fall Time                           |        | 3V <sub>P-P</sub> programmed V <sub>DLV</sub> = 0V, 10% to                                                                                                                                 | d, V <sub>DHV</sub> = 3V,<br>o 90%, trim condition                             | 500 | 650  | 800  | ps    |

|                                              |        | 5V <sub>P-P</sub> programmed, V <sub>DHV</sub> = 5V,<br>V <sub>DLV</sub> = 0V, 10% to 90% (Note 4)                                                                                         |                                                                                | 800 | 1000 | 1200 |       |

|                                              |        | $0.2V_{P-P}$ programm $V_{DLV} = 0V$ , 20% to                                                                                                                                              |                                                                                |     | ±40  |      |       |

| Rise-and-Fall Time Matching                  |        | 1V <sub>P-P</sub> programmed V <sub>DLV</sub> = 0V, 10% to                                                                                                                                 |                                                                                |     | ±50  | ±130 |       |

|                                              |        | 3V <sub>P-P</sub> programmed V <sub>DLV</sub> = 0V, 10% to                                                                                                                                 |                                                                                |     | ±50  | ±200 | ps    |

|                                              |        | 5V <sub>P-P</sub> programmed V <sub>DLV</sub> = 0V, 10% t                                                                                                                                  |                                                                                |     | ±50  |      |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$\begin{array}{l} (V_{CC}=9.75\text{V},\ V_{EE}=\text{-}4.75\text{V},\ V_{DD}=3.3\text{V},\ V_{HHP}=17.5\text{V},\ V_{DHV}=3\text{V},\ V_{DLV}=\text{0V},\ V_{DTV}=1.5\text{V},\ SC1=SC0=0\text{V},\ V_{CPHV}=7.2\text{V},\ V_{CPLV}=2.2\text{V},\ V_{CTV}=1.4\text{V},\ V_{BV}=4\text{V},\ V_{DGS}=V_{GND}=0\text{V},\ V_{CHV}=V_{IVMAX}=2\text{V},\ V_{CLV}=V_{IVMIN}=1\text{V},\ V_{COM}=2.5\text{V},\ V_{CLMPL}=0\text{V},\ V_{LDHV}=0\text{V},\ V_{LD}=2.5\text{V},\ V_{CLMPL}=2.5\text{V},\ V_{CLMPL}=2.5\text{V},$

| PARAMETER           | SYMBOL | CONDITIONS                                                                               |                                                                                                | MIN | TYP  | MAX  | UNITS |

|---------------------|--------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----|------|------|-------|

|                     |        |                                                                                          | SC1 = 0, SC0 = 1,<br>V <sub>DHV</sub> = 3V, V <sub>DLV</sub> =<br>0V, 20% to 80%               |     | 75   |      |       |

| Slew Rate           |        | Relative to SC1 = SC0 = 0                                                                | SC1 = 1, SC0 = 0,<br>V <sub>DHV</sub> = 3V, V <sub>DLV</sub> = 0V,<br>20% to 80%               |     | 50   |      | %     |

|                     |        |                                                                                          | SC1 = 1, SC0 = 1,<br>V <sub>DHV</sub> = 3V, V <sub>DLV</sub> = 0V,<br>20% to 80%               |     | 25   |      |       |

| Minimum Pulse Width |        |                                                                                          | 0.2V <sub>P-P</sub> programmed,<br>V <sub>DHV</sub> = 0.2V,<br>V <sub>DLV</sub> = 0V (Note 19) |     | 800  |      |       |

|                     |        | Positive or                                                                              | 1V <sub>P-P</sub> programmed,<br>V <sub>DHV</sub> = 1V, V <sub>DLV</sub> = 0V<br>(Note 19)     |     | 950  |      |       |

|                     |        | negative                                                                                 | 3V <sub>P-P</sub> programmed,<br>V <sub>DHV</sub> = 3V, V <sub>DLV</sub> = 0V<br>(Notes 4, 19) |     | 1000 | 1250 | ps    |

|                     |        |                                                                                          | 5V <sub>P-P</sub> programmed,<br>V <sub>DHV</sub> = 5V, V <sub>DLV</sub> = 0V<br>(Note 19)     |     | 1300 |      |       |

|                     |        | V <sub>DHV</sub> = 0.2\<br>= 0V<br>1V <sub>P-P</sub> program<br>V <sub>DHV</sub> = 1V, V | 0.2V <sub>P-P</sub> programmed,<br>V <sub>DHV</sub> _ = 0.2V, V <sub>DLV</sub> _<br>= 0V       |     | 1100 |      |       |

|                     |        |                                                                                          | 1V <sub>P-P</sub> programmed,<br>V <sub>DHV</sub> = 1V, V <sub>DLV</sub> = 0V                  |     | 900  |      |       |

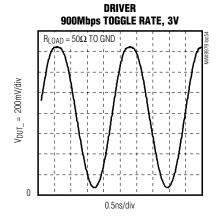

|                     |        | (Note 20)                                                                                | 3V <sub>P-P</sub> programmed,<br>V <sub>DHV</sub> = 3V, V <sub>DLV</sub> = 0V                  |     | 800  |      |       |

| Data Rate           |        |                                                                                          | 5V <sub>P-P</sub> programmed,<br>V <sub>DHV_</sub> = 5V, V <sub>DLV_</sub> = 0V                |     | 680  |      | Mbps  |

|                     |        |                                                                                          | 0.2V <sub>P-P</sub> programmed,<br>V <sub>DHV</sub> = 0.2V, V <sub>DLV</sub> = 0V              |     | 1200 |      |       |

|                     |        | То 90%р-р                                                                                | 1V <sub>P-P</sub> programmed,<br>V <sub>DHV</sub> = 1V, V <sub>DLV</sub> = 0V                  |     | 1100 |      |       |

|                     | 1)     | (Note 21)                                                                                | 3V <sub>P-P</sub> programmed,<br>V <sub>DHV</sub> = 3V, V <sub>DLV</sub> = 0V                  |     | 900  |      |       |

|                     |        |                                                                                          | 5V <sub>P-P</sub> programmed,<br>V <sub>DHV</sub> = 5V, V <sub>DLV</sub> = 0V                  |     | 720  |      |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$\begin{array}{l} (\text{V}_{\text{CC}} = 9.75\text{V}, \, \text{V}_{\text{EE}} = \text{-}4.75\text{V}, \, \text{V}_{\text{DD}} = 3.3\text{V}, \, \text{V}_{\text{HHP}} = 17.5\text{V}, \, \text{V}_{\text{DHV}} = 3\text{V}, \, \text{V}_{\text{DLV}} = 0\text{V}, \, \text{V}_{\text{DTV}} = 1.5\text{V}, \, \text{SC1} = \text{SC0} = 0\text{V}, \, \text{V}_{\text{CPHV}} = 7.2\text{V}, \, \text{V}_{\text{CPLV}} = 2.2\text{V}, \, \text{V}_{\text{CTV}} = 1.4\text{V}, \, \text{V}_{\text{BV}} = 4\text{V}, \, \text{V}_{\text{DGS}} = \text{V}_{\text{GND}} = 0\text{V}, \, \text{V}_{\text{CHV}} = \text{V}_{\text{IVMAX}} = 2\text{V}, \, \text{V}_{\text{CLV}} = \text{V}_{\text{IVMIN}} = 1\text{V}, \, \text{V}_{\text{COM}} = 2.5\text{V}, \, \text{V}_{\text{LDHV}} = 0\text{V}, \, \text{V}_{\text{LD}} = 0\text{V}, \, \text{V}_{\text{ID}} = 2.5\text{V}, \, \text{V}_{\text{CLAMPHI}} = 5\text{V}, \, \text{V}_{\text{CLAMPLO}} = 0\text{V}, \, \text{V}_{\text{HH}} = 10\text{V}, \, \text{CDRP} = 0\text{b001}, \, \text{RO} = 0\text{b1000}, \, \text{HYST} = 0\text{b000}, \, \text{Z}_{\text{LOAD}} = 50\Omega, \, \text{T}_{\text{J}} = +70^{\circ}\text{C} \, \text{to} \, \text{an accuracy of } \pm 15^{\circ}\text{C}, \, \text{unless otherwise noted}. \, \text{All temperature coefficients are measured at T}_{\text{J}} = +40^{\circ}\text{C} \, \text{to} \, +100^{\circ}\text{C}, \, \text{unless otherwise noted}. \, \text{(Note 1)} \end{array}$

| PARAMETER                                             | SYMBOL        |                                                          | CONDITIONS                                                                                                            |              | MIN  | TYP  | MAX  | UNITS             |

|-------------------------------------------------------|---------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------|------|------|------|-------------------|

| D: 15 11 7:                                           |               |                                                          | / <sub>DHV_</sub> = 3V, V <sub>DL</sub><br>red 10% to 90%                                                             |              | 300  | 500  | 1000 |                   |

| Rise-and-Fall Time                                    |               | Term to drive, \ = 1.5V, measu                           | Term to drive, V <sub>DHV</sub> = 3V, V <sub>DLV</sub> = 0V, V <sub>DTV</sub> = 1.5V, measured 10% to 90% of waveform |              |      |      | 850  | ps                |

| HIGH-SPEED COMPARATORS                                | •             |                                                          |                                                                                                                       |              |      |      |      | •                 |

| DC CHARACTERISTICS                                    |               |                                                          |                                                                                                                       |              |      |      |      |                   |

| Input-Voltage Range                                   |               | (Notes 2, 22)                                            |                                                                                                                       |              | -1.5 |      | +6.5 | V                 |

| Differential Input Voltage                            |               | V <sub>DUT</sub> - V <sub>CHV</sub>                      | , V <sub>DUT_</sub> - V <sub>CLV</sub>                                                                                | (Note 23)    |      |      | ±8   | V                 |

| Input Offset Voltage                                  |               | $V_{DUT_{-}} = 1.5V$                                     |                                                                                                                       |              |      | ±1   | ±5   | mV                |

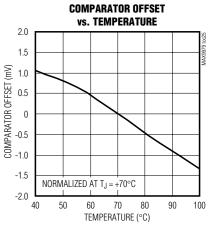

| Input-Voltage Temperature<br>Coefficient              |               | (Notes 4, 24)                                            |                                                                                                                       |              |      | ±50  | ±175 | μV°C              |

| Common-Mode Rejection Ratio                           | CMRR          | $V_{DUT_{-}} = -1.5V$                                    | , 6.5V (Note 25)                                                                                                      | )            | 50   | 55   |      | dB                |

| Linearity Frank (Nata OC)                             |               | 0 to 3V, V <sub>DUT</sub> = 0V, 1.5V, 3V                 |                                                                                                                       |              | ±1   | ±5   | \/   |                   |

| Linearity Error (Note 26)                             |               | Full range, V <sub>DU</sub>                              | Full range, V <sub>DUT</sub> = -1.5V, 0V, 1.5V, 3V, 6.5V                                                              |              |      | ±1   | ±10  | mV                |

| Power-Supply Rejection Ratio                          | PSRR          | V <sub>DUT</sub> _ = -1.5 a                              | and 6.5V (Notes                                                                                                       | 5, 27)       | 50   | 66   |      | dB                |

|                                                       |               | HYST0                                                    | HYST1                                                                                                                 | HYST2        |      |      |      |                   |

|                                                       |               | 0                                                        | 0                                                                                                                     | 0            |      | 0    |      |                   |

|                                                       |               | 0                                                        | 0                                                                                                                     | 1            |      | 2    |      |                   |

|                                                       |               | 0                                                        | 1                                                                                                                     | 0            |      | 4    |      |                   |

| Hysteresis                                            |               | 0                                                        | 1                                                                                                                     | 1            |      | 6    |      | mV                |

|                                                       |               | 1                                                        | 0                                                                                                                     | 0            |      | 8    |      |                   |

|                                                       |               | 1                                                        | 0                                                                                                                     | 1            |      | 10   |      |                   |

|                                                       |               | 1                                                        | 1                                                                                                                     | 0            |      | 12   |      |                   |

|                                                       |               | 1                                                        | 1                                                                                                                     | 1            |      | 15   |      |                   |

| AC CHARACTERISTICS (Notes 4                           | , 28, 29, 30) |                                                          |                                                                                                                       | •            |      |      |      |                   |

| Minimum Pulse Width                                   |               | (Note 31)                                                |                                                                                                                       |              |      | 0.50 | 0.65 | ns                |

| Propagation Delay                                     |               |                                                          |                                                                                                                       |              | 0.5  | 0.9  | 1.5  | ns                |

| Propagation-Delay Temperature<br>Coefficient          |               |                                                          |                                                                                                                       |              |      | 1.7  |      | ps/°C             |

| Propagation-Delay Match                               |               | High/low vs. lo                                          | ow/high, absolut                                                                                                      | te value of  |      | ±10  | ±25  | ps                |

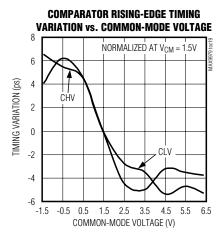

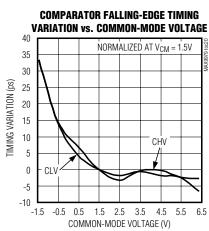

| Propagation-Delay Dispersion vs.<br>Common-Mode Input |               | -1.4V to +6.4V (Note 32)                                 |                                                                                                                       |              |      | 40   | 55   | ps <sub>P-P</sub> |

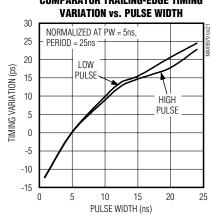

| Propagation-Delay Dispersion vs. Duty Cycle           |               | 0.6ns to 24.4ns pulse width, relative to 5ns pulse width |                                                                                                                       |              |      | ±25  | ±40  | ps                |

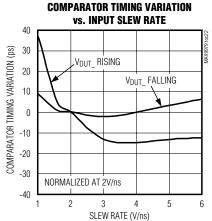

| Propagation-Delay Dispersion vs.<br>Slew Rate         |               | 1V/ns to 6V/ns                                           | , relative to 2V/                                                                                                     | ns (Note 33) |      | ±30  | ±55  | ps                |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 9.75\text{V}, V_{EE} = -4.75\text{V}, V_{DD} = 3.3\text{V}, V_{HHP} = 17.5\text{V}, V_{DHV} = 3\text{V}, V_{DLV} = 0\text{V}, V_{DTV} = 1.5\text{V}, SC1 = SC0 = 0\text{V}, V_{CPHV} = 7.2\text{V}, V_{CPLV} = -2.2\text{V}, V_{CTV} = 1.4\text{V}, V_{BV} = 4\text{V}, V_{DGS} = V_{GND} = 0\text{V}, V_{CHV} = V_{IVMAX} = 2\text{V}, V_{CLV} = V_{IVMIN} = 1\text{V}, V_{COM} = 2.5\text{V}, V_{LDHV} = 0\text{V}, V_{LDLV} = 0\text{V}, V_{IN} = 2.5\text{V}, V_{VIOS} = 0\text{V}, V_{IIOS} = 2.5\text{V}, V_{CLAMPHI} = 5\text{V}, V_{CLAMPLO} = 0\text{V}, V_{HH} = 10\text{V}, CDRP = 0\text{b001}, RO = 0\text{b1000}, HYST = 0\text{b000}, Z_{LOAD} = 50\Omega, T_{J} = +70^{\circ}\text{C} \text{ to an accuracy of } \pm 15^{\circ}\text{C}, \text{ unless otherwise noted}.$  All temperature coefficients are measured at  $T_{J} = +40^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$ , unless otherwise noted.) (Note 1)

| PARAMETER                                 | SYMBOL      | CONDITIONS                                                                              |                                  | MIN         | TYP         | MAX         | UNITS  |  |

|-------------------------------------------|-------------|-----------------------------------------------------------------------------------------|----------------------------------|-------------|-------------|-------------|--------|--|

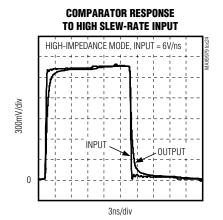

| Equivalent 20, 90 Bandwidth               |             | $V_{DTV} = 0.5V$ , driver termin                                                        | ated (Note 34)                   | 1000        | 1500        |             | MHz    |  |

| Equivalent 20–80 Bandwidth                |             | Driver high impedance                                                                   |                                  |             | 700         |             | IVI⊓∠  |  |

| Cable-Droop Compensation,                 |             | 1V swing, rise/fall time =                                                              | CDRP = 0b000                     |             | 0           |             | - %    |  |

| Peaking                                   |             | 500ps, DRV terminated                                                                   | CDRP = 0b111                     |             | 10          |             | 76     |  |

| LOGIC OUTPUTS (CH_, NCH_, C               | L_, NCL_ co | llector output, $R_L = 50\Omega$ into                                                   | ernal pullup to CT               | 'V)         |             |             |        |  |

| Termination Voltage                       | CTV_        |                                                                                         |                                  | 0           |             | 3.5         | V      |  |

| Output High Current                       |             |                                                                                         |                                  |             | 0           |             | mA     |  |

| Output Low Current                        |             |                                                                                         |                                  |             | 16          |             | mA     |  |

| Output-Voltage Compliance                 |             | Set by IOUT_, RTERM_ and \                                                              | /CTV                             | -0.5        |             | CTV_        | V      |  |

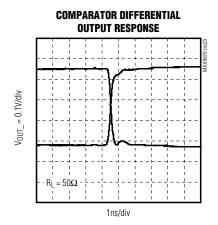

| Differential Rise Time                    |             | 20% to 80% (Note 4)                                                                     |                                  |             | 200         | 400         | ps     |  |

| Differential Fall Time                    |             | 20% to 80% (Note 4)                                                                     |                                  |             | 200         | 400         | ps     |  |

| Termination Resistor Value                |             | CTV_ to CH_, NCH_, CL_, N                                                               | NCL_                             | 48          |             | 52          | Ω      |  |

| Output High Voltage                       | VoH         | With output resistors, RTERN (Note 56)                                                  | <sub>M</sub> to V <sub>CTV</sub> | CTV 0.1     | CTV<br>0.02 | CTV_        | V      |  |

| Output Low Voltage                        | VoL         | With output resistors, R <sub>TERM</sub> to V <sub>CTV</sub> (Note 56)                  |                                  | CTV<br>0.55 | CTV 0.4     | CTV<br>0.35 | V      |  |

| Output-Voltage Swing                      |             | With output resistors, $50\Omega$ nominal trim (Note 56)                                |                                  | 350         | 400         | 450         | mV     |  |

| DYNAMIC CLAMPS                            |             |                                                                                         |                                  |             |             |             |        |  |

| CPHV_ Functional Clamp Range              |             | I <sub>DUT</sub> _ = -1mA, V <sub>CPLV</sub> _ = -1.                                    | 5V (Note 2)                      | -0.3        |             | +6.5        | V      |  |

| CPLV_Functional Clamp Range               |             | I <sub>DUT_</sub> = 1mA, V <sub>CPHV_</sub> = 6.5                                       | V (Note 2)                       | -1.5        |             | +5.3        | V      |  |

| CPHV_ Maximum Programmable Voltage        |             | I <sub>DUT</sub> _ = 0mA (Note 23)                                                      |                                  | 7.2         | 7.5         |             | V      |  |

| CPLV_ Minimum Programmable Voltage        |             | I <sub>DUT</sub> _ = 0mA (Note 23)                                                      |                                  |             | -2.5        | -2.2        | V      |  |

| O"                                        |             | IDUT_ = -1mA, VCPHV_ = 1.5\                                                             | /, V <sub>CPLV</sub> = -1.5V     |             |             | ±10         | .,     |  |

| Offset Voltage                            |             | I <sub>DUT_</sub> = 1mA, V <sub>CPLV_</sub> = 1.5                                       |                                  |             |             | ±10         | mV     |  |

| Offset-Voltage Temperature<br>Coefficient |             | VCPHV_ = VCPLV_ = 1.5V                                                                  |                                  |             | 0.5         |             | mV/°C  |  |

|                                           |             | I <sub>DUT</sub> = -1mA, V <sub>CPHV</sub> = 1.5<br>-1.5V (Note 5)                      | 5V, V <sub>CPLV</sub> =          | 40          |             |             |        |  |

| Power-Supply Rejection Ratio              |             | I <sub>DUT_</sub> = +1mA, V <sub>CPLV_</sub> = 1.5V, V <sub>CPHV_</sub> = 6.5V (Note 5) |                                  | 40          |             |             | dB     |  |

| High Clamp Voltage Gain                   |             | V <sub>CPHV</sub> = -0.3V, 6.5V                                                         |                                  | 0.998       |             | 1.002       | V/V    |  |

| Low Clamp Voltage Gain                    |             | V <sub>CPLV</sub> = -1.5V, 5.3V                                                         |                                  | 0.998       |             | 1.002       | V/V    |  |

| Voltage-Gain Temperature<br>Coefficient   |             | _                                                                                       |                                  |             | 100         |             | ppm/°C |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$\begin{array}{l} (V_{CC}=9.75\text{V},\ V_{EE}=\text{-}4.75\text{V},\ V_{DD}=3.3\text{V},\ V_{DHP}=17.5\text{V},\ V_{DHV}=3\text{V},\ V_{DLV}=\text{0V},\ V_{DTV}=1.5\text{V},\ SC1=SC0=\text{0V},\ V_{CPHV}=7.2\text{V},\ V_{CPLV}=\text{-}2.2\text{V},\ V_{CTV}=1.4\text{V},\ V_{BV}=4\text{V},\ V_{DGS}=V_{GND}=0\text{V},\ V_{CHV}=V_{IVMAX}=2\text{V},\ V_{CLV}=V_{IVMIN}=1\text{V},\ V_{COM}=2.5\text{V},\ V_{LDHV}=0\text{V},\ V_{LDLV}=0\text{V},\ V_{ID}=2.5\text{V},\ V_{VIOS}=0\text{V},\ V_{IDS}=2.5\text{V},\ V_{CLAMPHI}=5\text{V},\ V_{CLAMPLO}=0\text{V},\ V_{HH}=10\text{V},\ CDRP=0\text{bb001},\ RO=0\text{b1000},\ HYST=0\text{b000},\ Z_{LOAD}=50\Omega,\ T_{J}=+70^{\circ}\text{C}\ to\ an\ accuracy\ of\ \pm15^{\circ}\text{C},\ unless\ otherwise\ noted.\ All\ temperature\ coefficients\ are\ measured\ at\ T_{J}=+40^{\circ}\text{C}\ to\ +100^{\circ}\text{C},\ unless\ otherwise\ noted.) \label{eq:coefficients}$

| PARAMETER                                       | SYMBOL                    | CONDITIONS                                                                                                 | MIN   | TYP  | MAX   | UNITS  |

|-------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------|-------|------|-------|--------|

| Linearity                                       |                           | I <sub>DUT</sub> _ = -1mA, V <sub>CPHV</sub> _ = -0.3V, 1.5V, 3.25V, 5V, 6.5V                              |       |      | ±30   | mV     |

| Linearity                                       |                           | I <sub>DUT</sub> _ = 1mA, V <sub>CPLV</sub> _ = -1.5V, 0.5V, 2.25V, 4V, 5.3V                               |       |      | ±30   | IIIV   |

| Statio Output Current                           |                           | $V_{CPHV} = 0V$ , $V_{CPLV} = -1.5V$ , $R_L = 0\Omega$ to 6.5V                                             | -120  |      | -60   | m ^    |

| Static Output Current                           |                           | $V_{CPLV}$ = 5V, $V_{CPHV}$ = 6.5V, $R_L$ = $0\Omega$ to -1.5V                                             | 60    |      | 120   | mA     |

| High Clamp Resistance                           |                           | V <sub>CPHV</sub> = 0V, V <sub>CPLV</sub> = -1.5V, I <sub>DUT</sub> = -5mA and -15mA                       | 48    |      | 55    | Ω      |

| Low Clamp Resistance                            |                           | $V_{CPHV}$ = 6.5V, $V_{CPLV}$ = 0V, $I_{DUT}$ = 5mA and 15mA                                               | 48    |      | 55    | Ω      |

| High Clamp-Resistance Variation                 |                           | I <sub>DUT</sub> _ = -20mA and -30mA, V <sub>CPHV</sub> _ = 2.5V,<br>V <sub>CPLV</sub> _ = -1.5V (Note 35) |       | ±5   |       | Ω      |

| Low Clamp-Resistance Variation                  |                           | I <sub>DUT</sub> _ = 20mA and 30mA, V <sub>CPLV</sub> _ = 2.5V,<br>V <sub>CPHV</sub> _ = 6.5V (Note 35)    |       | ±5   |       | Ω      |

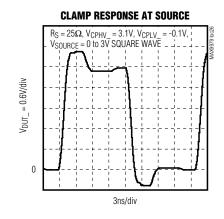

| Overshoot and Undershoot                        |                           | (Note 36)                                                                                                  |       | 700  |       | mV     |

| PARAMETRIC MEASUREMENT L                        | JNIT (PMU)                |                                                                                                            |       |      |       |        |

| DC ELECTRICAL CHARACTERIS                       | TICS                      |                                                                                                            |       |      |       |        |

| FORCE VOLTAGE ( $R_L \ge 10 M\Omega$ , V        | ı <sub>N_</sub> = 2.5V, u | nless otherwise noted)                                                                                     |       |      |       |        |

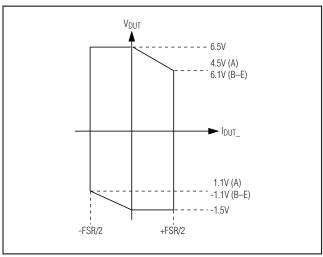

|                                                 |                           | $I_{DUT} = 0mA$                                                                                            | -1.5  |      | +6.5  |        |

|                                                 |                           | I <sub>DUT</sub> = +FSR/2, range A                                                                         | -1.5  |      | +4.5  |        |

| Force-Voltage Output Range                      | VIN                       | I <sub>DUT</sub> = +FSR/2, ranges B-E                                                                      | -1.5  |      | +6.1  | V      |

| (Note 2)                                        |                           | I <sub>DUT</sub> = -FSR/2, range A                                                                         | 1.1   |      | 6.5   |        |

|                                                 |                           | I <sub>DUT</sub> = -FSR/2, ranges B-E                                                                      | -1.1  |      | +6.5  |        |

| Force-Voltage Offset Error                      |                           | I <sub>DUT_</sub> = 0mA                                                                                    | -5    |      | +5    | mV     |

| Force-Voltage PSRR                              |                           | (Note 5)                                                                                                   | -5    |      | +5    | mV/V   |

| Force-Voltage Load Regulation                   |                           | IDUT_ = +FSR/2 to -FSR/2 using SENSE_<br>input                                                             |       | ±200 |       | μV     |

| Force-Voltage Offset<br>Temperature Coefficient |                           | (Note 37)                                                                                                  |       | ±50  |       | μV/°C  |

| Force-Voltage Gain Error                        |                           | $V_{IN} = -1.5V$ to +6.5V, nominal gain = +1                                                               | -0.1  |      | +0.1  | %      |

| Force-Voltage Gain Temperature<br>Coefficient   |                           | -                                                                                                          |       | ±10  |       | ppm/°C |

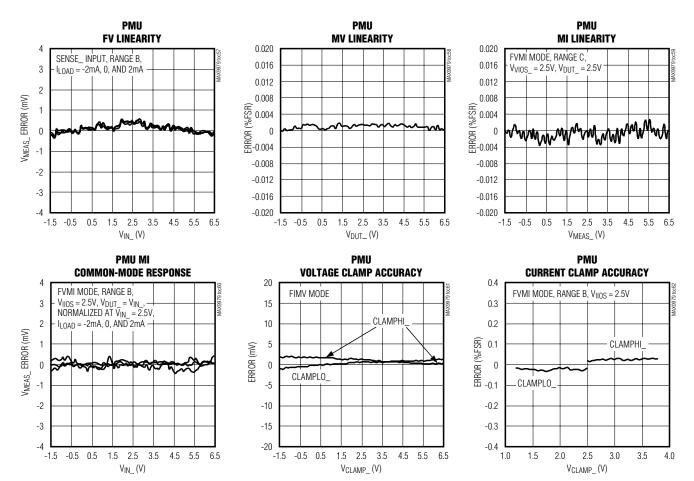

| Force-Voltage Linearity Error                   |                           | V <sub>IN</sub> = -1.5V, 0.5V, 2.5V, 4.5V, 6.5V<br>(Notes 38, 39)                                          | -0.02 |      | +0.02 | %FSR   |

\_ /VIXI/VI

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 9.75\text{V}, V_{EE} = -4.75\text{V}, V_{DD} = 3.3\text{V}, V_{HHP} = 17.5\text{V}, V_{DHV} = 3\text{V}, V_{DLV} = 0\text{V}, V_{DTV} = 1.5\text{V}, SC1 = SC0 = 0\text{V}, V_{CPHV} = 7.2\text{V}, V_{CPLV} = -2.2\text{V}, V_{CTV} = 1.4\text{V}, V_{BV} = 4\text{V}, V_{DGS} = V_{GND} = 0\text{V}, V_{CHV} = V_{IVMAX} = 2\text{V}, V_{CLV} = V_{IVMIN} = 1\text{V}, V_{COM} = 2.5\text{V}, V_{LDHV} = 0\text{V}, V_{LDLV} = 0\text{V}, V_{IN} = 2.5\text{V}, V_{VIOS} = 0\text{V}, V_{IIOS} = 2.5\text{V}, V_{CLAMPHI} = 5\text{V}, V_{CLAMPLO} = 0\text{V}, V_{HH} = 10\text{V}, CDRP = 0\text{b001}, RO = 0\text{b1000}, HYST = 0\text{b000}, Z_{LOAD} = 50\Omega, T_{J} = +70^{\circ}\text{C} \text{ to an accuracy of } \pm 15^{\circ}\text{C}, \text{ unless otherwise noted}.$  All temperature coefficients are measured at  $T_{J} = +40^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$ , unless otherwise noted.) (Note 1)

| PARAMETER                                                          | SYMBOL                    | CONDITIONS                                                                                                               | MIN   | TYP  | MAX   | UNITS         |  |

|--------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------|-------|------|-------|---------------|--|

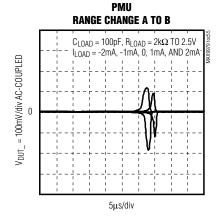

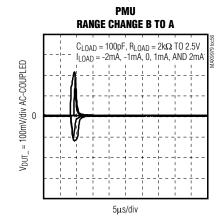

| Force-Voltage Range Switching<br>Glitch                            |                           | From any two adjacent ranges, C <sub>DUT</sub> = 100pF, I <sub>DUT</sub> = (±0.25 x FSR) of lower current range (Note 4) |       |      | 0.3   | V             |  |

| MEASURE CURRENT (Measured                                          | at MEAS_ ir               | r FIMI mode, V <sub>IN</sub> = V <sub>IIOS</sub> = V <sub>DUT</sub> = 2.5V)                                              |       |      |       |               |  |

| Measure-Current Offset                                             | I <sub>MOS</sub>          | (Note 38)                                                                                                                | -1    |      | +1    | %FSR          |  |

| Measure-Current PSRR                                               |                           | I <sub>DUT</sub> _ = 0mA (Note 5)                                                                                        | -0.05 |      | +0.05 | %FSR/V        |  |

| Measure-Current Offset<br>Temperature Coefficient                  |                           |                                                                                                                          |       | ±20  |       | ppmFSR/<br>°C |  |

| Manager Original Control                                           | 1                         | Ranges A, B, C                                                                                                           | -1.0  |      | +1.0  | 0/            |  |

| Measure-Current Gain Error                                         | I <sub>MGE</sub>          | Ranges D, E                                                                                                              | -1.1  |      | +1.1  | %             |  |

| Measure-Current Gain                                               |                           | Ranges B-E                                                                                                               |       | ±20  |       | nnm/0C        |  |

| Temperature Coefficient                                            |                           | Range A                                                                                                                  |       | +100 |       | ppm/°C        |  |

|                                                                    |                           | Ranges B-E, I <sub>DUT</sub> = -FSR/2, -FSR/4, 0, FSR/4, FSR/2 relative to end points                                    | -0.02 |      | +0.02 |               |  |

| Measure-Current Linearity Error (Note 38)                          | I <sub>MLER</sub>         | Range A, I <sub>DUT</sub> = -30mA, -15mA, 0, 15mA, 30mA, relative to end points                                          | -0.03 |      | +0.03 | %FSR          |  |

|                                                                    |                           | Range A, I <sub>DUT</sub> = -FSR/2, -FSR/4, 0, FSR/4, FSR/2 relative to end points                                       | -0.06 |      | +0.06 | =             |  |

| F0D.M. 0 1 11/1                                                    |                           | VIIOSMIN = 2V (Note 40)                                                                                                  |       | 6    |       |               |  |

| +FSR Measure Output Voltage                                        |                           | VIIOSMAX = 4V (Note 40)                                                                                                  |       | 8    |       | V             |  |

|                                                                    |                           | VIIOSMIN = 2V (Note 40)                                                                                                  |       | -2   |       |               |  |

| -FSR Measure Output Voltage                                        |                           | VIIOSMAX = 4V (Note 40)                                                                                                  |       | 0    |       | V             |  |

| Rejection of Output Measure Error Due to Common-Mode Sense Voltage | CMVR <sub>LER</sub>       | I <sub>DUT_</sub> = 0mA, V <sub>IN_</sub> = -1.5V to +6.5V, percent<br>FSR change at MEAS_ per volt change at DUT_       |       |      | 0.003 | %FSR/V        |  |

|                                                                    |                           | Range E, R_E = $500k\Omega$                                                                                              | -2    |      | +2    |               |  |

|                                                                    |                           | Range D, R_D = $50k\Omega$                                                                                               | -20   |      | +20   | μA            |  |

| Measure-Current Range (Note 2)                                     |                           | Range C, R_C = $5k\Omega$                                                                                                | -200  |      | +200  |               |  |

|                                                                    |                           | Range B, R_B = $500\Omega$                                                                                               | -2    |      | +2    | ^             |  |

|                                                                    |                           | Range A, R_A = 20Ω (Note 41)                                                                                             | -50   |      | +50   | mA            |  |

| FORCE CURRENT (V <sub>DUT</sub> = V <sub>IN</sub>                  | = V <sub>IIOS</sub> = 2.5 | V, unless otherwise noted)                                                                                               |       |      |       |               |  |

| Input-Voltage Range For Setting                                    |                           | VIIOSMIN = 2V                                                                                                            |       | 6    |       | V             |  |

| Force Current to +FSR/2                                            |                           | VIIOSMAX = 3.5V                                                                                                          |       | 7.5  |       | v v           |  |

| Input-Voltage Range For Setting                                    |                           | VIIOSMIN = 2V                                                                                                            |       | -2   |       | V             |  |

| Force Current to -FSR/2                                            |                           | VIIOSMAX = 3.5V                                                                                                          |       | -0.5 |       | v             |  |

| Current-Sense Amplifier Offset<br>Voltage Input                    |                           | Relative to V <sub>DGS</sub>                                                                                             | 2.0   | 2.5  | 3.5   | V             |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$\begin{array}{l} (\text{V}_{\text{CC}} = 9.75\text{V}, \, \text{V}_{\text{EE}} = \text{-}4.75\text{V}, \, \text{V}_{\text{DD}} = 3.3\text{V}, \, \text{V}_{\text{HHP}} = 17.5\text{V}, \, \text{V}_{\text{DHV}} = 3\text{V}, \, \text{V}_{\text{DLV}} = 0\text{V}, \, \text{V}_{\text{DTV}} = 1.5\text{V}, \, \text{SC1} = \text{SC0} = 0\text{V}, \, \text{V}_{\text{CPHV}} = 7.2\text{V}, \, \text{V}_{\text{CPLV}} = 2.2\text{V}, \, \text{V}_{\text{CTV}} = 1.4\text{V}, \, \text{V}_{\text{BV}} = 4\text{V}, \, \text{V}_{\text{DGS}} = \text{V}_{\text{GND}} = 0\text{V}, \, \text{V}_{\text{CHV}} = \text{V}_{\text{IVMAX}} = 2\text{V}, \, \text{V}_{\text{CLV}} = \text{V}_{\text{IVMIN}} = 1\text{V}, \, \text{V}_{\text{COM}} = 2.5\text{V}, \, \text{V}_{\text{LDHV}} = 0\text{V}, \, \text{V}_{\text{LD}} = 0\text{V}, \, \text{V}_{\text{LD}} = 0\text{V}, \, \text{V}_{\text{LD}} = 2.5\text{V}, \, \text{V}_{\text{CLMPH}} = 5\text{V}, \, \text{V}_{\text{CLMPLO}} = 0\text{V}, \, \text{V}_{\text{HH}} = 10\text{V}, \, \text{CDRP} = 0\text{b001}, \, \text{RO} = 0\text{b1000}, \, \text{HYST} = 0\text{b000}, \, \text{Z}_{\text{LOAD}} = 50\Omega, \, \text{T}_{\text{J}} = +70^{\circ}\text{C} \, \text{to an accuracy of } \pm 15^{\circ}\text{C}, \, \text{unless otherwise noted}. \, \text{All temperature coefficients are measured at T}_{\text{J}} = +40^{\circ}\text{C} \, \text{to } +100^{\circ}\text{C}, \, \text{unless otherwise noted}. \, \text{(Note 1)} \end{array}$

| PARAMETER                                                 | SYMBOL      | CONDITIONS                                                                                                             | MIN       | TYP             | MAX    | UNITS         |

|-----------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|--------|---------------|

| Force-Current Offset                                      |             | (Note 38)                                                                                                              | -0.1      |                 | +0.1   | %FSR          |

| Force-Current Offset PSRR                                 |             | (Note 5)                                                                                                               | -0.2      |                 | +0.2   | %FSR/V        |

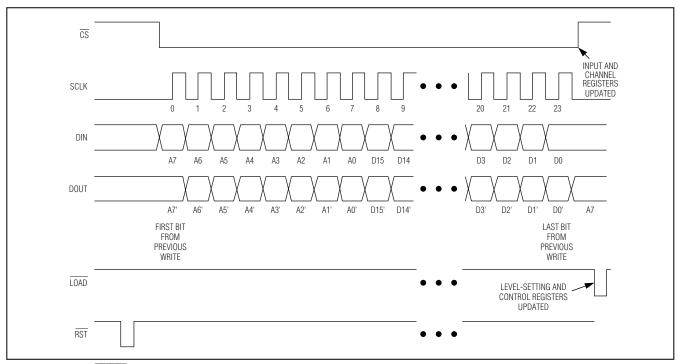

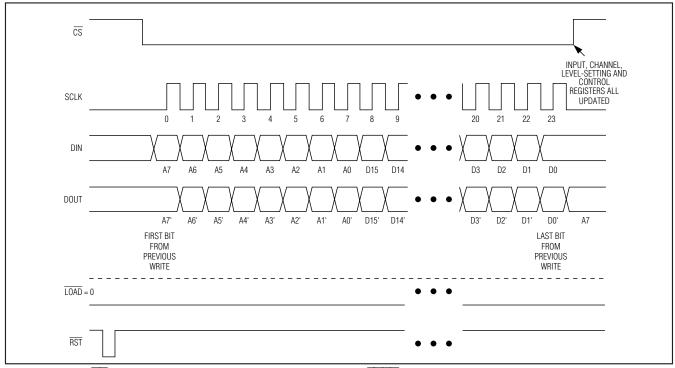

| Force-Current Offset-Temperature Coefficient              |             | (Note 37)                                                                                                              |           | ±20             |        | ppmFSR/<br>°C |