# **MK6116**

# MK6116, MKI6116, MK6116L, MKI6116L (N/S) - 15/20/25 2 K X 8 CMOS STATIC RAM

- BYTEWYDE™ 2K x 8 CMOS STATIC RAM.

- +5 VOLT ONLY WRITE/READ.

- 24-PIN 600 MIL PLASTIC DIP, JEDEC PINOUT 28-PIN 330 MIL SOIC.

- EQUAL WRITE AND READ CYCLE TIMES.

- HIGH PERFORMANCE WITH LOW CMOS STANDBY POWER.

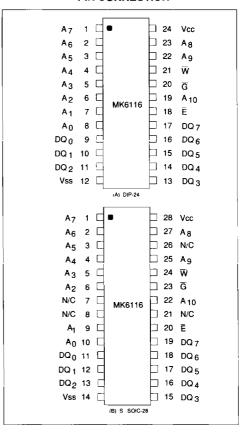

#### PIN CONNECTION

#### DESCRIPTION

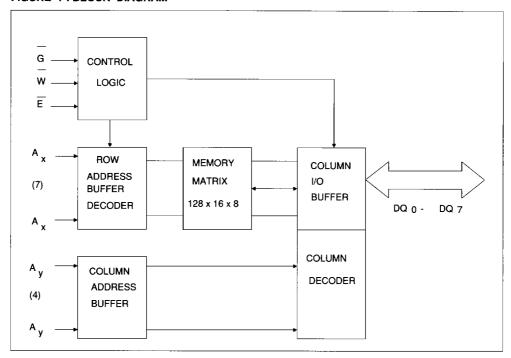

The MK6116 is a 16,384-bit CMOS Static RAM, organized as 2K x 8 usingSGS-THOMSON Microelectronics' advanced HCMOS process technology. This device is directly compatible with the popular 24-pin, three-wire handshake, 16K static CMOS RAM. All inputs and outputs are TTL compatible using a single 5V supply. The MK6116 provides full static operation, requiring no clocks or refresh operations, and has equal access and cycle times. Additionally, whenever E (Chip Enable) goes high, the device will maintain a reduced power standby mode until E again goes active low. (Refer to the MK6116Truth Table.)

### **PIN NAMES**

| A <sub>0</sub> -A <sub>10</sub>   | ADDRESS INPUTS |

|-----------------------------------|----------------|

| DQ <sub>0</sub> - DQ <sub>7</sub> | DATA I/O       |

| Ē                                 | CHIP ENABLE    |

| G                                 | OUTPUT ENABLE  |

| w                                 | WRITE ENABLE   |

| Vcc. Vss                          | +5V, GND       |

October 1989

1/9

FIGURE 1: BLOCK DIAGRAM

#### MK6116 TRUTH TABLE

| Ē               | G               | $\overline{\mathbf{w}}$ | MODE     | DQ      | POWER   |

|-----------------|-----------------|-------------------------|----------|---------|---------|

| VIH             | x               | Х                       | deselect | Hight Z | Standby |

| V <sub>IL</sub> | Х               | VIL                     | Write    | Din     | Active  |

| V <sub>IL</sub> | VIL             | V <sub>IH</sub>         | Read     | Dout    | Active  |

| V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub>         | Read     | Hight Z | Active  |

#### **READ MODE**

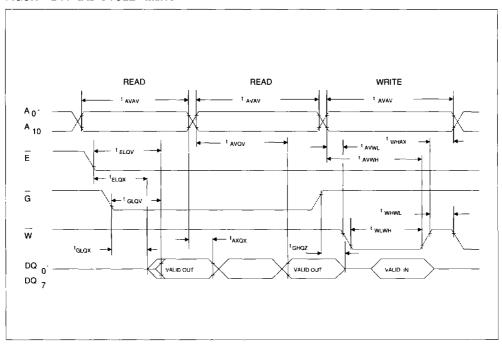

The MK6116 is in the read mode whenever  $\overline{W}$  (Write Enable) is high and  $\overline{E}$  (Chip Enable) is low, providing a ripple-through access of data from eight of 16,384 locations in the static storage array. Thus, the unique address specified by the 11 Address lnputs (A<sub>0</sub>-A<sub>10</sub>) defines which one of 2048 bytes of data is to be accessed.

Valid data will be available at the eight Data Outputs Drivers (DQ<sub>0</sub>-DQ<sub>7</sub>) within t<sub>AVQV</sub> after the last address input signal is stable, provided that the  $\overline{E}$  and  $\overline{G}$  (Qut-put Enable) access times are satisfied. If  $\overline{E}$  or  $\overline{G}$  access times are not met, data access will be measured from the limiting parameter ( $t_{ELQV}$  or  $t_{GLQV}$ ) rather than address. The state of the eight Data I/O signals is controlled by the  $\overline{E}$  and  $\overline{G}$  input signals. Data Out may be indeterminate between  $t_{AXQX}$  and  $t_{AVQV}$ , but data will always be valid at  $t_{AVQV}$ .

## AC ELECTRICAL CHARACTERISTICS (READ CYCLE)

$\{0^{\circ}C \le TA \le +70^{\circ}C \text{ (MK6116/L)}, -40^{\circ}C \le TA \le +105^{\circ}C \text{ (MKI6116/L)}, VCC = 5.0 +/-10\%\}$

| ALT.<br>Symbol   | STD.<br>SYMBOL    | PARAMETER                   | MKI6116 -15<br>MK6116L-15 |     |     |     |     |     | -     |       |

|------------------|-------------------|-----------------------------|---------------------------|-----|-----|-----|-----|-----|-------|-------|

|                  |                   |                             | MIN                       | MAX | MIN | MAX | MIN | MAX | UNITS | NOTES |

| t <sub>RC</sub>  | tavav             | Read Cycle Time             | 150                       |     | 200 |     | 250 |     | ns    |       |

| taa              | tavov             | Address Access Time         |                           | 150 |     | 200 |     | 250 | ns    | 1     |

| t <sub>CEA</sub> | tELOV             | ChipEnable Access Time      |                           | 150 |     | 200 |     | 250 | ns    | 1     |

| t <sub>CEZ</sub> | 1 <sub>EHOZ</sub> | Chip Enable Data OffTime    |                           | 35  |     | 40  |     | 50  | ns    |       |

| toea             | tGLQV             | Output Enable Access Time   |                           | 75  |     | 80  |     | 90  | ns    | 1     |

| toez             | tGLQV             | Output Enable Data Off Time |                           | 35  |     | 40  |     | 50  | ns    |       |

| toel             | tglax             | Out put Enable to Q Low-Z   | 15                        |     | 15  |     | 15  |     | ns    |       |

| toel             | tELQX             | Chip Enable to Q Low-Z      | 15                        |     | 15  |     | 15  |     | ns    |       |

| tон              | taxqx             | Output Hold from Address    | 15                        |     | 15  |     | 15  |     | ns    | 1     |

### FIGURE 2: READ CYCLE TIMING

#### WRITE MODE

The MK6116 is in the Write Mode of operation whenever W and E are active low (G is a don't care as noted in the Truth\_Table). The latter occurring falling edge of either W or E will determine the start of the write cycle. Therefore, address setup time and write or chip enable pulse width are referenced to the latter occurring edge of W or E. The write cycle can be terminated by either earlier rising edge of W or E. The addresses must be held valid

throughout the cycle. W must return to the high logic state for a minimum write recovery time designated as twhwl between write cycles. Addresses must remain valid for twhax at the termination of the write cycle. The same principles apply for an E controlled write cycle.

If the output bus has been enabled ( $\overline{E}$  and  $\overline{G}$  active low), then  $\overline{W}$  will disable the outputs within  $t_{WLOZ}$  from its falling edge; however, care must be taken to avoid a potential bus contention. Data-In must be valid  $t_{DVWH}$  or  $t_{DVEH}$  prior to the earlier rising

## AC ELECTRICAL CHARACTERISTICS (WRITE CYCLE)

$\{0^{\circ}C \le T_{A} \le +70^{\circ}C \text{ (MK6116/L)}, -40^{\circ}C \le T_{A} \le +105^{\circ}C \text{ (MKI6116/L)}, V_{CC}=5.0 \pm 10\%\}$

| ALT.<br>SYMBOL  | SDT.<br>SYMBOL    | PARAMETER                     | MK611<br>MK161<br>MK611<br>MK161 | 16 -15 | MK6116 - 20<br>MKI6116 -20<br>MK6116L-20<br>MKI6116L -20 |     | 20 MKI6116 -2<br>20 MKL6116-2 |     |       |       |

|-----------------|-------------------|-------------------------------|----------------------------------|--------|----------------------------------------------------------|-----|-------------------------------|-----|-------|-------|

|                 |                   |                               | MIN                              | MAX    | MIN                                                      | MAX | MIN                           | MAX | UNITS | NOTES |

| twc             | tavav             | Write Cycle Time              | 150                              |        | 200                                                      |     | 250                           |     | ns    |       |

| tas             | tavwl             | Address Setup Time W Low      | 0                                |        | 0                                                        |     | 0                             |     | ns    |       |

| tas             | taveL             | Address Setup Time E Low      | 0                                |        | 0                                                        |     | 0                             |     | ns    |       |

| tcew            | telen             | Chip Enable to End of Write   | 90                               |        | 120                                                      |     | 160                           |     | ns    |       |

| taw             | tavwh             | Address Valid to End of Write | 120                              |        | 140                                                      |     | 180                           |     | ns    |       |

| taw             | taven             | Address Valid to End of Write | 120                              |        | 140                                                      |     | 180                           |     | ns    |       |

| twew            | tww               | Write Pulse Width             | 90                               |        | 120                                                      |     | 160                           |     | ns    |       |

| tah             | twhax             | W Hight to address Change     | 10                               |        | 10                                                       |     | 10                            |     | ns    |       |

| tah             | tehax             | E Hight to address Change     | 10                               |        | 10                                                       |     | 10                            |     | ns    |       |

| twn             | twnwL             | W Hight to W Low Next Cycle   | 10                               |        | 10                                                       |     | 10                            |     | ns    |       |

| twez            | tw.caz            | W Data Off Time               |                                  | 50     |                                                          | 60  |                               | 80  | ns    |       |

| tcez            | tenoz             | E Data Off Time               |                                  | 50     |                                                          | 60  |                               | 80  | ns    |       |

| tos             | tovwh             | Data Setup Time to w Hight    | 40                               |        | 60                                                       |     | 100                           |     | ns    |       |

| t <sub>DS</sub> | toven             | Data Setup Time to E Hight    | 40                               |        | 60                                                       |     | 100                           |     | ns    |       |

| tрн             | twnox             | Data Hold Time W High         | 0                                |        | 0                                                        |     | 0                             |     | ns    |       |

| ton             | t <sub>EHDX</sub> | Data Hold Time E High         | 0                                |        | 0                                                        |     | 0                             |     | ns    | _     |

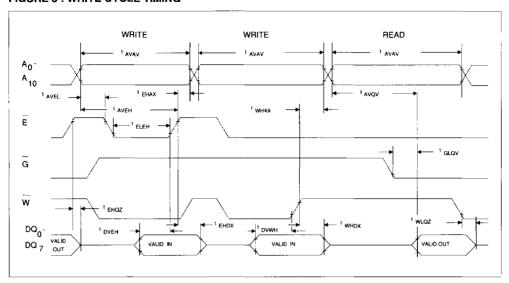

#### FIGURE 3: WRITE CYCLE TIMING

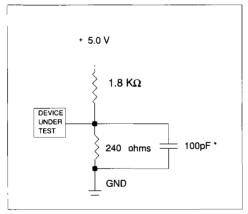

### FIGURE 4: OUTPUT LOAD DIAGRAM

\*Notes: Including scope and JIG

### **AC TEST CONDITION**

Input Levels: . . . . . . . 0.6 V to 2.4 V

Transition Times: . . . . . 5 ns

Input and Output Timing

Reference Levels: . . . . 0.8V or 2.2 V

## ABOLUTE MAXIMUM RATINGS

| PARAMETER                              | VALUES       | UNITS |

|----------------------------------------|--------------|-------|

| Voltage on any Pin Relative tro Ground | -0.3 to +7.0 | V     |

| Operating Temperature (MK6116L)        | 0 to +7      | °C    |

| Operatting Temperature (MKI6116/L)     | -40 to +150  | °C    |

| Storage Temperature                    | -55 to +150  | .C    |

| Power Dissipation                      | 1            | W     |

| Output Current                         | † 20         | mA    |

<sup>\*</sup> This is a stress rating only and functional operation of the device at these or any conditions above those indicazted in the operation section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

#### RECOMMENDED DC OPERATING CONDITIONS

$\{0^{\circ}C \le T_{A} \le +70^{\circ}C \text{ (MK6116/L)}, -40^{\circ}C \le T_{A} \le +150^{\circ}C \text{ (MK16116/L)}, V_{CC}=5.0 \text{ +/-} 10\%\}$

| SYMBOL          | PARAMETER          | MIN  | мах                  | UNITS | NOTES |

|-----------------|--------------------|------|----------------------|-------|-------|

| V <sub>CC</sub> | Supply Voltage     | 4.5  | 5.5.                 | V     | 4     |

| Vss             | Supply Voltage     | 0    | 0                    | V     | 4     |

| VIH             | Logic 1 All Inputs | 2.2  | V <sub>cc</sub> +0.3 | v     | 4     |

| VIL             | Logic 1 All Inputs | -0.3 | 0.8                  | v     | 4,5   |

### DC ELECTRICAL CHARACTERISTICS

$\{0^{\circ}C \leq TA \leq +70^{\circ}C \text{ (MK6116/L)}, -40^{\circ}C \leq T_{A} \leq +150^{\circ}C \text{ (MKI6116/L)}, V_{CC}=5.0 \text{ +/- }10\%\}$

| SYMBOL                                            | PARAMETER                                          | MIN | MAX | UNITS | NOTES |

|---------------------------------------------------|----------------------------------------------------|-----|-----|-------|-------|

|                                                   | Average V <sub>CC</sub> Power Supply Current,      |     | 70  |       |       |

| lcc                                               | MK6116, MKI6116                                    |     | 70  | mA    | 6     |

|                                                   | MK6116L, MKI6116L                                  |     | 70  | mA    |       |

| I <sub>SB1</sub>                                  | TTL Standby Current (E = V <sub>IH)</sub>          |     | 3   | mA    |       |

| CMOS Standby Current (E ≥ V <sub>CC</sub> -0.2 V) |                                                    |     |     | mA    |       |

| I <sub>SB2</sub>                                  | MK6116, MKI6116                                    |     | 1   |       |       |

| 'SB2                                              | MK6116L                                            |     |     | μА    |       |

|                                                   | MKI6116L                                           |     | 10  | μΑ    |       |

| ł <sub>LI</sub>                                   | Input Leakage Current                              | -1  | +1  | μА    | 7     |

| ILO                                               | Output Leakage Current                             | -5  | +5  | μA    | 7     |

| V <sub>OH</sub>                                   | Output Logic 1 Voltage (I <sub>OH</sub> = -1.0 mA) | 2.4 |     | V     |       |

| VoL                                               | Output Logic 2 Voltage (I <sub>OH</sub> = 2.1 mA)  |     | 0.4 | V     |       |

Output current absolute maximun rating is specified for one output at a time, not to exceed a duration of a1 second.

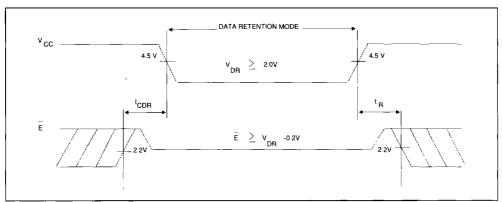

# LOW V<sub>CC</sub> Data RETENTION CHARACTERISTICS (MK6116L, MKI6116L)

| SYMBOL                              | PARAMETER                               | MIN   | MAX                   | UNITS | NOTES |

|-------------------------------------|-----------------------------------------|-------|-----------------------|-------|-------|

| V <sub>DR</sub>                     | V <sub>CC</sub> Data retention          | 2.0   | V <sub>CC</sub> (max) |       |       |

| Data Retention Power Supply Current |                                         |       |                       | 6     |       |

| IccDR                               | MK6116L                                 |       | '                     | μА    | 8     |

|                                     | MKI6116L                                |       | 3                     | μА    |       |

| todr                                | Chip Deselection to Data Retention Time | 0     |                       | ns    |       |

| t <sub>R</sub>                      | Operation Recovery Time                 | tavav |                       |       |       |

<sup>\*</sup> tAVAV = Read Cycle Time

### FIGURE 5 . LOW VCC DATA RETENTION TIMING

#### NOTES:

- 1. Measured with load as shown in Figure 4.

- 2 . Effective capacitance calculated from the equation: C= I\Delta V.\Delta V, with \Delta V = 3 volts and power supply at nominal level

- 3. Output is deselected.

- 4 All voltages referenced to GND

- 5. Negative spikes of -1.0 volts allowed for up to 10 ns once per cycle.

- 6 . ICC1 measured with output open

- 7 . Measured with GND ≤ V ≤ V<sub>CC</sub> and outputs deselected.

- 8 .  $V_{\text{CC}}$  = 2.0 Volts.

### CAPACITANCE (TA = 25°C)

| SYMBOL          | PARAMETER                           | MAX  | UNITS          | NOTES |

|-----------------|-------------------------------------|------|----------------|-------|

| Cı              | Capacitance on all pins (except DQ) | 7.0  | P <sup>F</sup> | 2     |

| C <sub>DQ</sub> | Capacitance on DQ pins              | 10.0 | P <sup>F</sup> | 2, 3  |

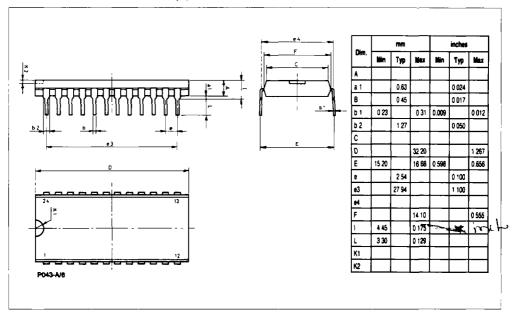

FIGURE 6. 24-PIN PLASTIC DIP (N)

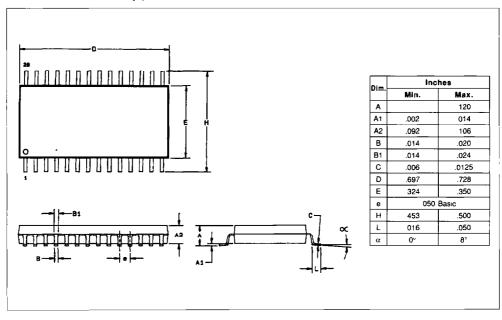

# FIGURE 7. 28-PIN SOIC (S)

### ORDERING INFORMATION

| PART NO.            | ACCESS TIME | CYCLE TIME | PACKAGE TYPE     | TEMPERATURE    |

|---------------------|-------------|------------|------------------|----------------|

| MK6116 (N/S)-15     | 150 ns      | 150 ns     | Plastic DIP/SOIC | 0°C to 70°C    |

| MK6116 (N)-20       | 200 ns      | 200 ns     | Plastic DIP      | 0°C to 70°C    |

| MK6116 (N) -25      | 250 ns      | 250 ns     | Plastic DIP      | 0°C to 70°C    |

| MKI6116 (N/S) -15   | 150 ns      | 150 ns     | Plastic DIP/SOIC | -40°C to 105°C |

| MKI6116 (N) -20     | 200 ns      | 200 ns     | Plastic DIP      | -40°C to 105°C |

| MKI6116 (N) - 25    | 250 ns      | 250 ns     | Plastic DIP      | -40°C to 105°C |

| MK6116 L(N/S) -15   | 150 ns      | 150 ns     | Plastic DIP/SOIC | 0°C to 70°C    |

| MK6116 L(N) - 20    | 200 ns      | 200 ns     | Plastic DIP      | 0°C to 70°C    |

| MK6116 L(N) - 25    | 250 ns      | 250 ns     | Plastic DIP      | 0°C to 70°C    |

| MKI6116 L(N/S) - 15 | 150 ns      | 150 ns     | Plastic DIP/SOIC | -40°C to 105°C |

| MKI6116L (N) - 20   | 200 ns      | 200 ns     | Plastic DIP      | -40°C to 105°C |

| 1K    |          | Commercial Temperature Range (0 $^{\circ}$ C to +70 $^{\circ}$ C) |

|-------|----------|-------------------------------------------------------------------|

| MKI   |          | Industrial Temperature Range (-40°C to +85°C)                     |

| 6116_ |          | Device Family and Identification Number                           |

|       | L        | Low Power                                                         |

|       | N        | Plastic Dip Package                                               |

|       | S        | SOIC Package                                                      |

|       | 15/20/25 | Speed Grade                                                       |

|       |          |                                                                   |

BYTEWYDE is a Trademark of SGS-THOMSON Microelectronics