# **Hardware Data Sheet**

Section I – EtherCAT Slave Controller Technology

Section II – EtherCAT Slave Controller Register Description

Section III – ET1100 Hardware Description: Pinout, Interface description, electrical and mechanical specification, ET1100 register overview

Version 1.8 Date: 2010-05-03

LEGAL NOTICE

#### Trademarks

Beckhoff<sup>®</sup>, TwinCAT<sup>®</sup>, EtherCAT<sup>®</sup>, Safety over EtherCAT<sup>®</sup>, TwinSAFE<sup>®</sup> and XFC<sup>®</sup> are registered trademarks of and licensed by Beckhoff Automation GmbH. Other designations used in this publication may be trademarks whose use by third parties for their own purposes could violate the rights of the owners.

#### **Patent Pending**

The EtherCAT Technology is covered, including but not limited to the following German patent applications and patents: DE10304637, DE102004044764, DE102005009224, DE102007017835 with corresponding applications or registrations in various other countries.

#### Disclaimer

The documentation has been prepared with care. The products described are, however, constantly under development. For that reason the documentation is not in every case checked for consistency with performance data, standards or other characteristics. In the event that it contains technical or editorial errors, we retain the right to make alterations at any time and without warning. No claims for the modification of products that have already been supplied may be made on the basis of the data, diagrams and descriptions in this documentation.

#### Copyright

#### © Beckhoff Automation GmbH 05/2010.

The reproduction, distribution and utilization of this document as well as the communication of its contents to others without express authorization are prohibited. Offenders will be held liable for the payment of damages. All rights reserved in the event of the grant of a patent, utility model or design.

# DOCUMENT HISTORY

| Version | Comment                                                                                         |

|---------|-------------------------------------------------------------------------------------------------|

| 0.6     | Initial release (Section I V0.0, Section II V1.0, Section III V0.6)                             |

| 0.7     | Section update (Section I V0.0, Section II V1.3, Section III V0.7)                              |

| 1.0     | Section update (Section I V1.0, Section II V1.5, Section III V1.0)                              |

| 1.1     | Section update (Section I V1.1, Section II V1.6, Section III V1.1)                              |

| 1.2     | Section update (Section I V1.2, Section II V1.7, Section III V1.2)                              |

| 1.2.1   | Section I update V1.2.1                                                                         |

| 1.3     | Section update (Section I V1.3, Section II V1.8, Section III V1.3), document organization added |

| 1.4     | Section update (Section I V1.6, Section II V2.0, Section III V1.4)                              |

| 1.5     | Section update (Section I V1.7, Section II V2.1, Section III V1.5)                              |

| 1.6     | Section update (Section II V2.2, Section III V1.6)<br>Update to ET1100-0002                     |

| 1.7     | Section update (Section III V1.7)                                                               |

| 1.8     | Section update (Section I V1.9, Section II V2.4, Section III V1.8)                              |

## DOCUMENT ORGANIZATION

The Beckhoff EtherCAT Slave Controller (ESC) documentation covers the following Beckhoff ESCs:

- ET1200

- ET1100

- EtherCAT IP Core for Altera® FPGAs

- EtherCAT IP Core for Xilinx<sup>®</sup> FPGAs

- ESC20

The documentation is organized in three sections. Section I and section II are common for all Beckhoff ESCs, Section III is specific for each ESC variant.

## Section I – Technology (All ESCs)

Section I deals with the basic EtherCAT technology. Starting with the EtherCAT protocol itself, the frame processing inside EtherCAT slaves is described. The features and interfaces of the physical layer with its two alternatives Ethernet and EBUS are explained afterwards. Finally, the details of the functional units of an ESC like FMMU, SyncManager, Distributed Clocks, Slave Information Interface, Interrupts, Watchdogs, and so on, are described.

Since Section I is common for all Beckhoff ESCs, it might describe features which are not available in a specific ESC. Refer to the feature details overview in Section III of a specific ESC to find out which features are available.

# Section II – Register Description (All ESCs)

Section II contains detailed information about all ESC registers. This section is also common for all Beckhoff ESCs, thus registers, register bits, or features are described which might not be available in a specific ESC. Refer to the register overview and to the feature details overview in Section III of a specific ESC to find out which registers and features are available.

## Section III – Hardware Description (Specific ESC)

Section III is ESC specific and contains detailed information about the ESC features, implemented registers, configuration, interfaces, pinout, usage, electrical and mechanical specification, and so on. Especially the Process Data Interfaces (PDI) supported by the ESC are part of this section.

## **Additional Documentation**

Additional documentation and utilities like application notes and Excel sheets for ET1100/ET1200 pinout configuration can be found at the Beckhoff homepage (<u>http://www.beckhoff.com</u> – Download/Documentation/EtherCAT development products).

# **Hardware Data Sheet**

# **Section I – Technology**

EtherCAT Protocol, Ethernet and EBUS Physical Layer, EtherCAT Processing Unit, FMMU, SyncManager, ESI EEPROM, Distributed Clocks, etc.

Version 1.9 Date: 2010-05-03

#### Trademarks

Beckhoff<sup>®</sup>, TwinCAT<sup>®</sup>, EtherCAT<sup>®</sup>, Safety over EtherCAT<sup>®</sup>, TwinSAFE<sup>®</sup> and XFC<sup>®</sup> are registered trademarks of and licensed by Beckhoff Automation GmbH. Other designations used in this publication may be trademarks whose use by third parties for their own purposes could violate the rights of the owners.

#### **Patent Pending**

The EtherCAT Technology is covered, including but not limited to the following German patent applications and patents: DE10304637, DE102004044764, DE102005009224, DE102007017835 with corresponding applications or registrations in various other countries.

#### Disclaimer

The documentation has been prepared with care. The products described are, however, constantly under development. For that reason the documentation is not in every case checked for consistency with performance data, standards or other characteristics. In the event that it contains technical or editorial errors, we retain the right to make alterations at any time and without warning. No claims for the modification of products that have already been supplied may be made on the basis of the data, diagrams and descriptions in this documentation.

#### Copyright

#### © Beckhoff Automation GmbH 05/2010.

The reproduction, distribution and utilization of this document as well as the communication of its contents to others without express authorization are prohibited. Offenders will be held liable for the payment of damages. All rights reserved in the event of the grant of a patent, utility model or design.

#### Comment Version 1.0 Initial release Chapter Interrupts – AL Event Request: corrected AL Event Mask register 1.1 • address to 0x0204:0x0207 EtherCAT Datagram: Circulating Frame bit has position 14 (not 13) . PHY addressing configuration changed Loop control: a port using Auto close mode is automatically opened if a valid Ethernet frame is received at this port EEPROM read/write/reload example: steps 1 and 2 swapped EEPROM: Configured Station Alias (0x0012:0x0013) is only taken over at first EEPROM load after power-on or reset SyncManager: Watchdog trigger and interrupt generation in mailbox mode with . single byte buffers requires alternating write and read accesses for some ESCs, thus buffered mode is required for Digital I/O watchdog trigger generation National Semiconductor DP83849I Ethernet PHY deprecated because of large • link loss reaction time and delay Added distinction between permanent ports and Bridge port (frame processing) Added PDI chapter PDI and DC Sync/Latch signals are high impedance until the ESI EEPROM is successfully loaded Editorial changes 1.2 PHY address configuration revised. Refer to Section III for ESC supported . configurations Added Ethernet Link detection chapter Added MI Link Detection and Configuration, link detection descriptions updated Added EEPROM Emulation for EtherCAT IP Core Added General Purpose Input chapter Corrected minimum datagram sizes in EtherCAT header figure Editorial changes Chapter 5.1.1: incompatible PHYs in footnote 1 deleted 1.2.1 Added advisory for unused MII/RMII/EBUS ports 1.3 • Ethernet PHY requirements revised: e.g., configuration by strapping options, recommendations enhanced. Footnote about compatible PHYs removed, information has moved to the EtherCAT Slave Controller application note "PHY Selection Guide". Frame Error detection chapter enhanced FIFO size reduction chapter enhanced EBUS enhanced link detection chapter enhanced Ethernet PHY link loss reaction time must be faster than 15 µs, otherwise use Enhanced link detection Enhanced link detection description corrected. Enhanced link detection does not remain active if it is disabled by EEPROM and EBUS handshake frames are received ARMW/FRWM commands increase the working counter by 1 Editorial changes Update to EtherCAT IP Core Release 2.1.0/2.01a 1.4 Added restriction to enhanced link configuration: RX ER has to be asserted outside of frames (IEEE802 optional feature) ESC power-on sequence for IP Core corrected Removed footnote on t<sub>Diff</sub> figures, refer to Section III for actual figures Editorial changes

# DOCUMENT HISTORY

| Version | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.5     | <ul> <li>EEPROM Read/Write/Reload example: corrected register addresses</li> <li>Updated/clarified PHY requirements, PHY link loss reaction time is mandatory</li> <li>Enhanced Link Detection can be configured port-wise depending on ESC</li> <li>Added DC Activation and DC Activation State features for some ESCs</li> <li>ESC10 removed</li> <li>Editorial changes</li> </ul>                                                                                                                                                                                                                                                                                                       |

| 1.6     | <ul> <li>Fill reserved EEPROM words of the ESC Configuration Area with 0</li> <li>Interrupt chapter: example for proper interrupt handling added</li> <li>Use Position Addressing only for bus scanning at startup and to detect newly attached devices</li> <li>System Time PDI controlled: detailed description added</li> <li>Added MII back-to-back connection example</li> <li>Renamed Err(x) LED to PERR(x)</li> <li>Editorial changes</li> </ul>                                                                                                                                                                                                                                    |

| 1.7     | <ul> <li>Link status description enhanced</li> <li>Clarifications for DC System Time and reference between clocks and registers</li> <li>Chapter on avoiding unconnected Port 0 configurations added</li> <li>Direct ESC to standard Ethernet MAC MII connection added</li> <li>MI link detection and configuration must not be used without LINK_MII signals</li> <li>Added criteria for detecting when DC synchronization is established</li> <li>ESI EEPROM interface is a point-to-point connection</li> <li>PHY requirements: PHY startup should not rely on MDC clocking, ESD tolerance and baseline wander compensation recommendations added</li> <li>Editorial changes</li> </ul> |

| 1.8     | <ul> <li>Update to EtherCAT IP Core Release 2.3.0/2.03a</li> <li>EEPROM acknowledge error (0x0502[13]) can also occur for a read access</li> <li>ERR and STATE LED updated</li> <li>Editorial changes</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.9     | <ul> <li>EtherCAT state machine: additional AL status codes defined</li> <li>EtherCAT protocol: LRD/LRW read data depends on bit mask</li> <li>Updated EBUS Enhanced Link Detection</li> <li>Updated FMMU description</li> <li>Loop control description updated</li> <li>EtherCAT frame format (VLAN tag) description enhanced</li> <li>Update to EtherCAT IP Core Release 2.3.2/2.03c</li> </ul>                                                                                                                                                                                                                                                                                          |

## CONTENTS

| 1 | EtherCAT S  | Slave Con  | troller Ove | erview                              | 1  |

|---|-------------|------------|-------------|-------------------------------------|----|

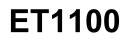

|   | 1.1         | EtherCA    | T Slave C   | Controller Function Blocks          | 2  |

|   | 1.2         | Further    | Reading o   | on EtherCAT and ESCs                | 3  |

|   | 1.3         | Scope o    | of Section  | I                                   | 3  |

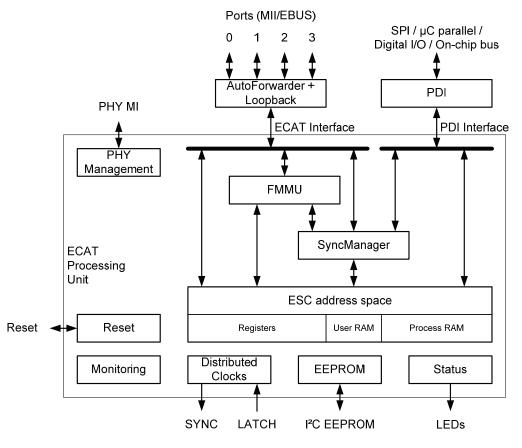

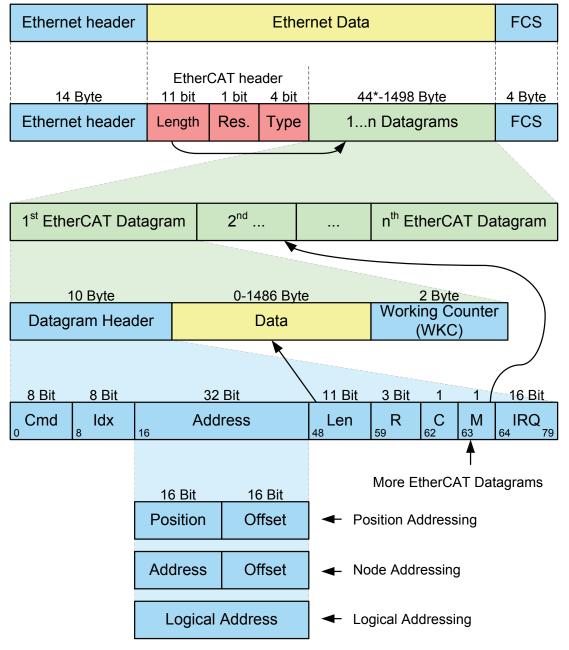

| 2 | EtherCAT I  | Protocol   |             |                                     | 4  |

|   | 2.1         | EtherCA    | T Header    |                                     | 4  |

|   | 2.2         | EtherCA    | T Datagra   | am                                  | 5  |

|   | 2.3         | EtherCA    | T Addres    | sing Modes                          | 6  |

|   |             | 2.3.1      | Device A    | Addressing                          | 7  |

|   |             | 2.3.2      | Logical     | Addressing                          | 7  |

|   | 2.4         | Working    | Counter     |                                     | 8  |

|   | 2.5         | EtherCA    | T Comma     | and Types                           | 9  |

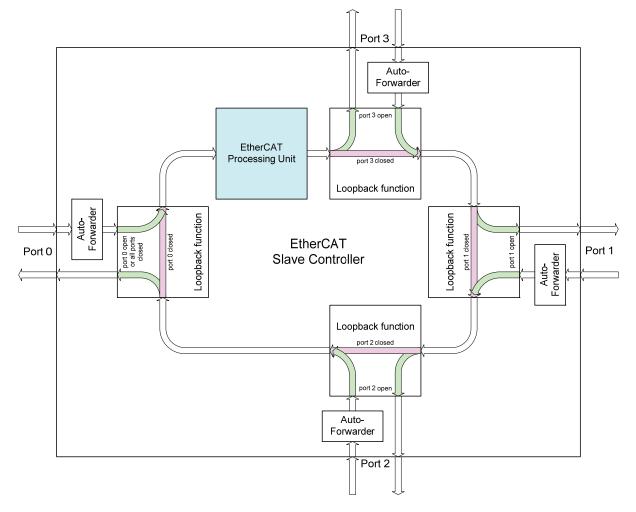

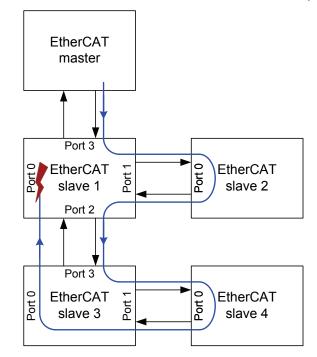

| 3 | Frame Proc  | cessing    |             |                                     | 11 |

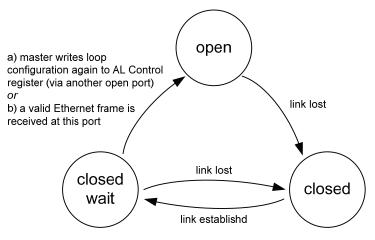

|   | 3.1         | Loop Co    | ontrol and  | Loop State                          | 11 |

|   | 3.2         | Frame F    | Processing  | Order                               | 14 |

|   | 3.3         | Perman     | ent Ports   | and Bridge Port                     | 15 |

|   | 3.4         | Shadow     | Buffer for  | Register Write Operations           | 15 |

|   | 3.5         | Circulati  | ng Frame    | s                                   | 15 |

|   |             | 3.5.1      | Unconne     | ected Port 0                        | 16 |

|   | 3.6         | Non-Eth    | erCAT Pr    | otocols                             | 16 |

|   | 3.7         | Special    | Functions   | of Port 0                           | 16 |

| 4 | Physical La | yer Comr   | non Featu   | ires                                | 17 |

|   | 4.1         | Link Sta   | tus         |                                     | 17 |

|   | 4.2         | Selectin   | g Standar   | d/Enhanced Link Detection           | 18 |

|   | 4.3         | FIFO Siz   | ze Reduct   | ion                                 | 19 |

|   | 4.4         | Frame E    | Error Dete  | ction                               | 19 |

| 5 | Ethernet Pl | nysical La | yer         |                                     | 20 |

|   | 5.1         | Require    | ments to B  | Ethernet PHYs                       | 20 |

|   | 5.2         | MII Inter  | face Sign   | als                                 | 22 |

|   | 5.3         | RMII Int   | erface Sig  | nals                                | 24 |

|   | 5.4         | Link Det   | tection     |                                     | 25 |

|   |             | 5.4.1      | LINK_M      | II Signal                           | 25 |

|   |             | 5.4.2      | MI Link     | Detection and Configuration         | 25 |

|   | 5.5         | Standar    | d and Enh   | anced MII Link Detection            | 26 |

|   | 5.6         | MII Man    | agement     | Interface (MI)                      | 26 |

|   |             | 5.6.1      | PHY Ad      | dressing/PHY Address Offset         | 27 |

|   |             | 5.6.2      | Logical     | nterface                            | 28 |

|   |             |            | 5.6.2.1     | MI read/write example               | 28 |

|   |             |            | 5.6.2.2     | MI Interface Assignment to ECAT/PDI | 28 |

|   |             | 5.6.3     | MI Proto    | col                                              | 29 |

|---|-------------|-----------|-------------|--------------------------------------------------|----|

|   |             | 5.6.4     | Timing s    | pecifications                                    | 29 |

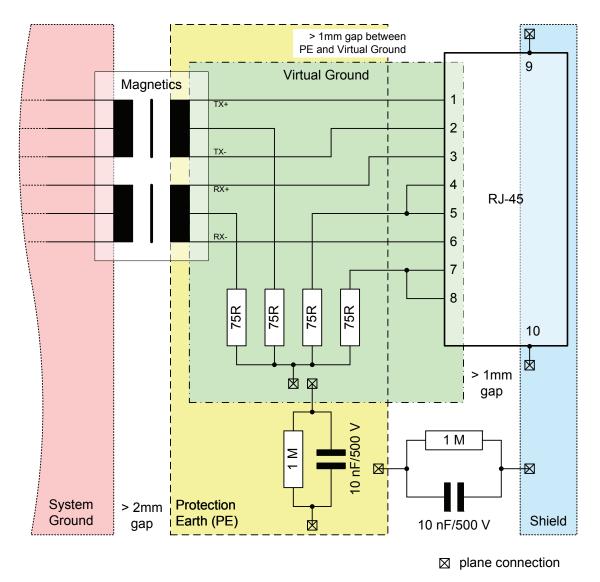

|   | 5.7         | Ethernet  | Terminat    | ion and Grounding Recommendation                 | 30 |

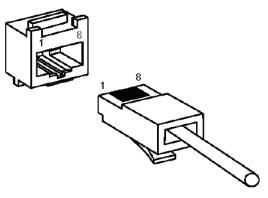

|   | 5.8         | Ethernet  | Connecto    | or (RJ45 / M12)                                  | 31 |

|   | 5.9         | Back-to-  | Back MII (  | Connection                                       | 32 |

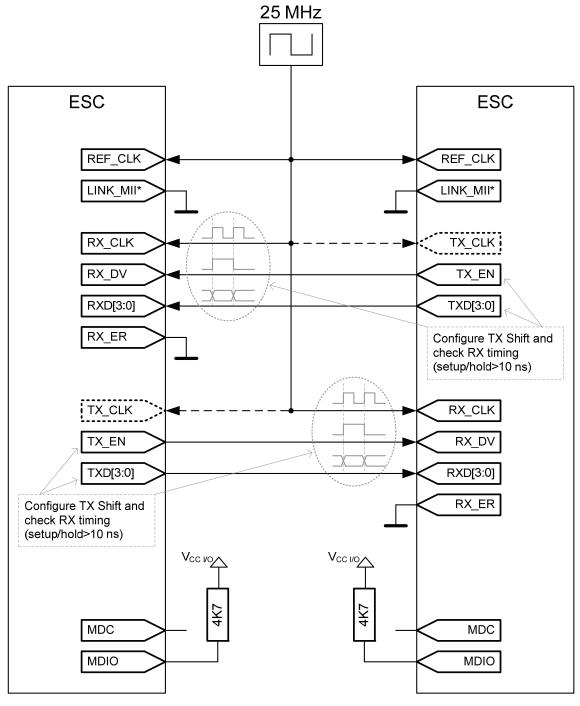

|   |             | 5.9.1     | ESC to E    | ESC Connection                                   | 32 |

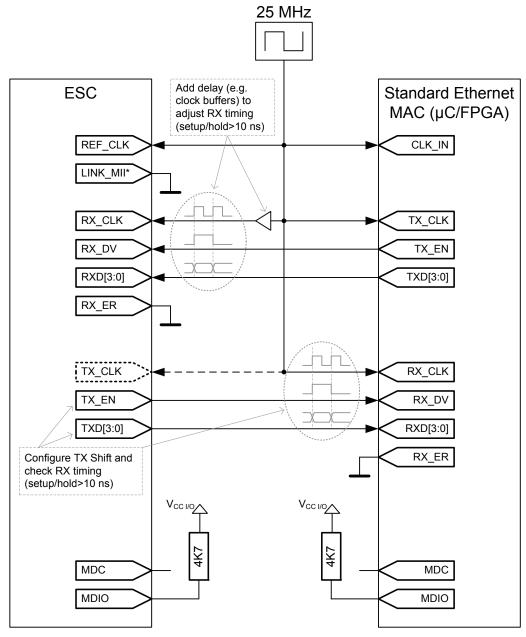

|   |             | 5.9.2     | ESC to S    | Standard Ethernet MAC                            | 33 |

| 6 | EBUS/LVD    | S Physica | l Layer     |                                                  | 34 |

|   | 6.1         | Interface | ;           |                                                  | 34 |

|   | 6.2         | EBUS P    | rotocol     |                                                  | 35 |

|   | 6.3         | Timing C  | Characteris | stics                                            | 35 |

|   | 6.4         | Standard  | d EBUS Li   | nk Detection                                     | 36 |

|   | 6.5         | Enhance   | ed EBUS L   | ink Detection                                    | 36 |

|   | 6.6         | EBUS R    | X Errors    |                                                  | 37 |

|   | 6.7         | EBUS Lo   | ow Jitter   |                                                  | 37 |

|   | 6.8         | EBUS C    | onnection   |                                                  | 37 |

| 7 | FMMU        |           |             |                                                  | 38 |

| 8 | SyncManag   | er        |             |                                                  | 40 |

|   | 8.1         | Buffered  | Mode        |                                                  | 41 |

|   | 8.2         | Mailbox   | Mode        |                                                  | 42 |

|   |             | 8.2.1     | Mailbox     | Communication Protocols                          | 42 |

|   | 8.3         | Interrupt | and Wate    | hdog Trigger Generation, Latch Event Generation  | 43 |

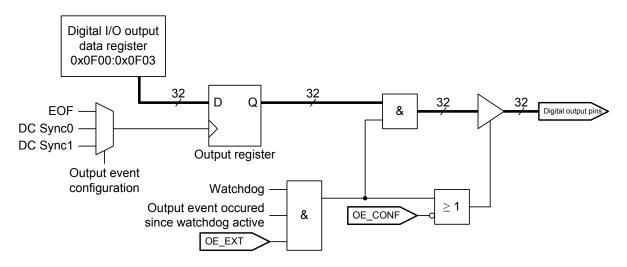

|   | 8.4         | Single B  | yte Buffer  | Length / Watchdog Trigger for Digital Output PDI | 43 |

|   | 8.5         | Repeatir  | ng Mailbox  | Communication                                    | 44 |

|   | 8.6         | SyncMa    | nager Dea   | activation by the PDI                            | 44 |

| 9 | Distributed | Clocks    |             |                                                  | 45 |

|   | 9.1         | Clock Sy  | nchroniza/  | ation                                            | 45 |

|   |             | 9.1.1     | Clock Sy    | nchronization Process                            | 47 |

|   |             | 9.1.2     | Propaga     | tion Delay Measurement                           | 48 |

|   |             |           | 9.1.2.1     | Propagation Delay Measurement Example            | 48 |

|   |             | 9.1.3     | Offset Co   | ompensation                                      | 52 |

|   |             | 9.1.4     | Drift Con   | npensation                                       | 53 |

|   |             | 9.1.5     | Reference   | ce between DC Registers/Functions and Clocks     | 54 |

|   |             | 9.1.6     | When is     | Synchronization established?                     | 55 |

|   |             | 9.1.7     | •           | nchronization Initialization Example             | 55 |

|   | 9.2         |           |             | atchSignals                                      | 56 |

|   |             | 9.2.1     | Interface   |                                                  | 56 |

|   |             | 9.2.2     | Configur    |                                                  | 56 |

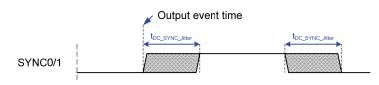

|   |             | 9.2.3     |             | nal Generation                                   | 57 |

|   |             |           | 9.2.3.1     | Cyclic Generation                                | 58 |

|   |             |           | 9.2.3.2     | Single Shot Mode                                 | 58 |

|    |             |           | 9.2.3.3               | Cyclic Acknowledge Mode               | 58 |

|----|-------------|-----------|-----------------------|---------------------------------------|----|

|    |             |           | 9.2.3.4               | Single Shot Acknowledge Mode          | 58 |

|    |             |           | 9.2.3.5               | SYNC1 Generation                      | 59 |

|    |             |           | 9.2.3.6               | SyncSignal Initialization Example     | 60 |

|    |             | 9.2.4     | LatchSig              | gnals                                 | 60 |

|    |             |           | 9.2.4.1               | Single Event Mode                     | 61 |

|    |             |           | 9.2.4.2               | Continuous Mode                       | 61 |

|    |             |           | 9.2.4.3               | SyncManager Event                     | 61 |

|    |             | 9.2.5     | ECAT or               | r PDI Control                         | 61 |

|    | 9.3         | System    | Time PDI              | Controlled                            | 62 |

|    | 9.4         | Commu     | nication T            | iming                                 | 64 |

| 10 | EtherCAT S  | State Mac | hine                  |                                       | 66 |

|    | 10.1        | EtherCA   | AT State M            | lachine Registers                     | 67 |

|    |             | 10.1.1    | AL Cont               | rol and AL Status Register            | 67 |

|    |             | 10.1.2    | Device E              | Emulation                             | 67 |

|    |             | 10.1.3    | Error Inc             | lication and AL Status Code Register  | 68 |

|    | 10.2        | State M   | achine Se             | rvices                                | 70 |

| 11 | ESI EEPRC   | M         |                       |                                       | 71 |

|    | 11.1        | ESI EEI   | PROM Co               | ntent                                 | 72 |

|    | 11.2        | ESI EEI   | PROM Log              | gical Interface                       | 73 |

|    |             | 11.2.1    | ESI EEF               | PROM Errors                           | 74 |

|    |             |           | 11.2.1.1              | Missing Acknowledge                   | 75 |

|    |             | 11.2.2    | ESI EEF               | PROM Interface Assignment to ECAT/PDI | 75 |

|    |             | 11.2.3    | Read/W                | rite/Reload Example                   | 76 |

|    |             | 11.2.4    |                       | M Emulation                           | 76 |

|    | 11.3        |           |                       | ctrical Interface (I <sup>2</sup> C)  | 77 |

|    |             | 11.3.1    | Word Ac               | ddressing                             | 77 |

|    |             | 11.3.2    | EEPRO                 |                                       | 77 |

|    |             | 11.3.3    | I <sup>2</sup> C Acce | ess Protocol                          | 78 |

|    |             |           | 11.3.3.1              | Write Access                          | 78 |

|    |             |           | 11.3.3.2              | Read Access                           | 79 |

|    |             | 11.3.4    | Timing s              | specifications                        | 79 |

| 12 | Interrupts  |           |                       |                                       | 81 |

|    | 12.1        |           |                       | t (PDI Interrupt)                     | 81 |

|    | 12.2        | ECAT E    | ivent Requ            | uest (ECAT Interrupt)                 | 82 |

|    | 12.3        | Clearing  | g Interrupts          | s Accidentally                        | 82 |

| 13 | Watchdogs   |           |                       |                                       | 83 |

|    |             |           | Data Wa               | tchdog                                | 83 |

|    |             | PDI Wa    | tchdog                |                                       | 83 |

| 14 | Error Count |           |                       |                                       | 84 |

|    | 14.1        | Frame e   | error detec           | tion                                  | 85 |

|    |             |           |                       |                                       |    |

|    | 14.2          | Errors and Forwarded Errors                          | 85 |

|----|---------------|------------------------------------------------------|----|

| 15 | LED Signals   | s (Indicators)                                       | 86 |

|    | 15.1          | RUN LED                                              | 86 |

|    | 15.2          | ERR LED                                              | 86 |

|    | 15.3          | STATE LED and STATE_RUN LED Signal                   | 86 |

|    | 15.4          | LINKACT LED                                          | 86 |

|    | 15.5          | Port Error LED (PERR)                                | 86 |

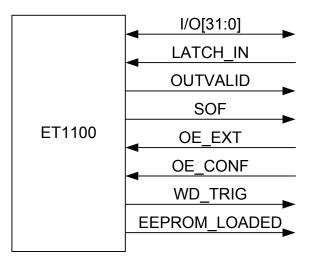

| 16 | Process Da    | ta Interface (PDI)                                   | 87 |

|    | 16.1          | PDI Selection and Configuration                      | 87 |

|    | 16.2          | General Purpose I/O                                  | 88 |

|    |               | 16.2.1 General Purpose Inputs                        | 88 |

|    |               | 16.2.2 General Purpose Output                        | 88 |

| 17 | Additional Ir | nformation                                           | 89 |

|    | 17.1          | ESC Clock Source                                     | 89 |

|    | 17.2          | Power-on Sequence                                    | 89 |

|    | 17.3          | Write Protection                                     | 90 |

|    |               | 17.3.1 Register Write Protection                     | 90 |

|    |               | 17.3.2 ESC Write Protection                          | 90 |

|    | 17.4          | ESC Reset                                            | 90 |

| 18 | Appendix      |                                                      | 91 |

|    | 18.1          | Support and Service                                  | 91 |

|    |               | 18.1.1 Beckhoff's branch offices and representatives | 91 |

|    | 18.2          | Beckhoff Headquarters                                | 91 |

# TABLES

| Table 1: ESC Main Features                                                                |    |

|-------------------------------------------------------------------------------------------|----|

| Table 2: EtherCAT Frame Header                                                            |    |

| Table 3: EtherCAT Datagram                                                                | 6  |

| Table 4: EtherCAT Addressing Modes                                                        | 6  |

| Table 5: Working Counter Increment                                                        | 8  |

| Table 6: EtherCAT Command Types                                                           |    |

| Table 7: EtherCAT Command Details                                                         |    |

| Table 8: Registers for Loop Control and Loop/Link Status                                  | 13 |

| Table 9: Frame Processing Order                                                           | 14 |

| Table 10: Link Status Description                                                         | 17 |

| Table 11: Registers for Enhanced Link Detection                                           | 19 |

| Table 12: MII Interface signals                                                           | 22 |

| Table 13: Special/Unused MII Interface signals                                            | 23 |

| Table 14: RMII Interface signals                                                          | 24 |

| Table 15: Registers used for Ethernet Link Detection                                      | 25 |

| Table 16: PHY Address configuration matches PHY address settings                          | 27 |

| Table 17: PHY Address configuration does not match actual PHY address settings            | 27 |

| Table 18: MII Management Interface Register Overview                                      | 28 |

| Table 19: MII Management Interface timing characteristics                                 | 29 |

| Table 20: Signals used for Fast Ethernet                                                  | 31 |

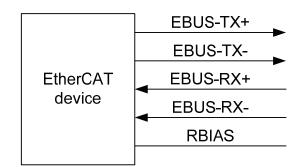

| Table 21: EBUS Interface signals                                                          | 34 |

| Table 22: EBUS timing characteristics                                                     |    |

| Table 23: Example FMMU Configuration                                                      | 38 |

| Table 24: SyncManager Register overview                                                   |    |

| Table 25: EtherCAT Mailbox Header                                                         |    |

| Table 26: Registers for Propagation Delay Measurement                                     |    |

| Table 27: Parameters for Propagation Delay Calculation                                    |    |

| Table 28: Registers for Offset Compensation                                               |    |

| Table 29: Registers for Drift Compensation                                                |    |

| Table 30: Reference between DC Registers/Functions and Clocks                             | 54 |

| Table 31: Distributed Clocks signals                                                      |    |

| Table 32: SyncSignal Generation Mode Selection                                            |    |

| Table 33: Registers for SyncSignal Generation                                             |    |

| Table 34: Registers for Latch Input Events                                                |    |

| Table 35: Registers for the EtherCAT State Machine                                        |    |

| Table 36: AL Control and AL Status Register Values                                        |    |

| Table 37: AL Status Codes (0x0134:0x0135)                                                 |    |

| Table 38: State Machine Services                                                          |    |

| Table 39: ESC Configuration Area                                                          |    |

| Table 40: ESI EEPROM Content Excerpt                                                      |    |

| Table 41: ESI EEPROM Interface Register Overview                                          |    |

| Table 42: ESI EEPROM Interface Errors                                                     |    |

| Table 43: I <sup>2</sup> C EEPROM signals                                                 |    |

| Table 44: EEPROM Size                                                                     |    |

| Table 45: I <sup>2</sup> C Control Byte                                                   |    |

| Table 46: I <sup>2</sup> C Write Access                                                   |    |

| Table 47: I <sup>2</sup> C Read Access                                                    |    |

| Table 48: EEPROM timing characteristics                                                   |    |

| Table 49: Registers for AL Event Request Configuration                                    |    |

| Table 50: Registers for ECAT Event Request Configuration                                  |    |

| Table 51: Registers for Watchdogs                                                         |    |

| Table 52: Error Counter Overview                                                          |    |

| Table 53: Errors Detected by Physical Layer, Auto-Forwarder, and EtherCAT Processing Unit |    |

| Table 54: RUN LED States.                                                                 |    |

| Table 55: LINKACT LED States                                                              |    |

| Table 56: Available PDIs depending on ESC                                                 |    |

| Table 57: ESC Power-On Sequence                                                           |    |

| Table 58: Registers for Write Protection                                                  |    |

| <u> </u>                                                                                  | -  |

# FIGURES

| Figure 1: EtherCAT Slave Controller Block Diagram                        | 1  |

|--------------------------------------------------------------------------|----|

| Figure 2: Ethernet Frame with EtherCAT Data                              |    |

| Figure 3: EtherCAT Datagram                                              | 5  |

| Figure 4: Auto close loop state transitions                              | 12 |

| Figure 5: Frame Processing                                               | 14 |

| Figure 6: Circulating Frames                                             |    |

| Figure 7: All frames are dropped because of Circulating Frame Prevention | 16 |

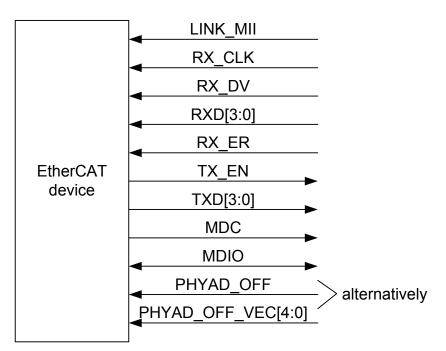

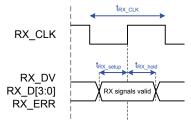

| Figure 8: MII Interface signals                                          | 22 |

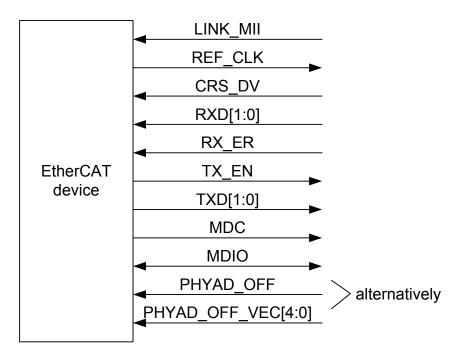

| Figure 9: RMII Interface signals                                         |    |

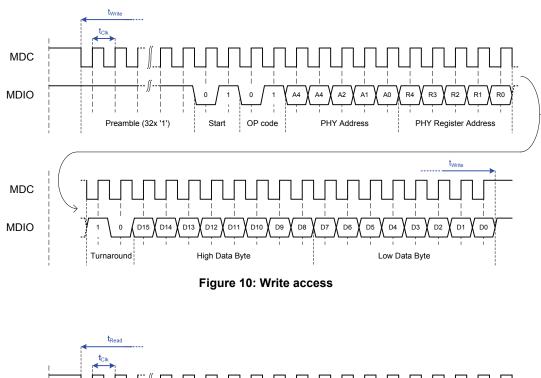

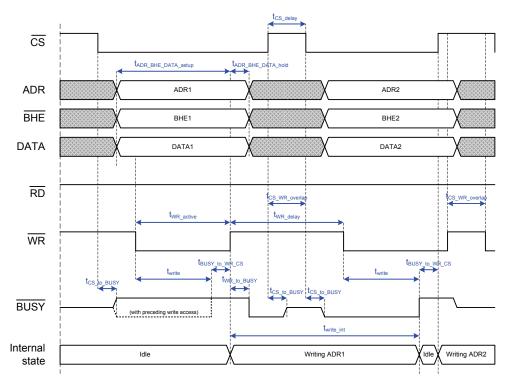

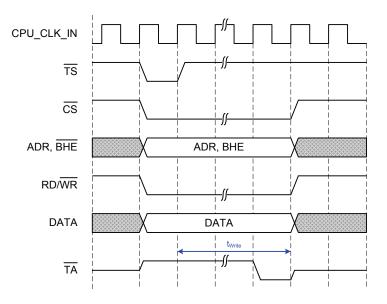

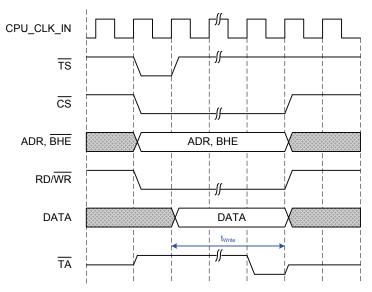

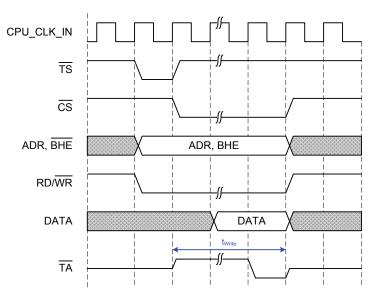

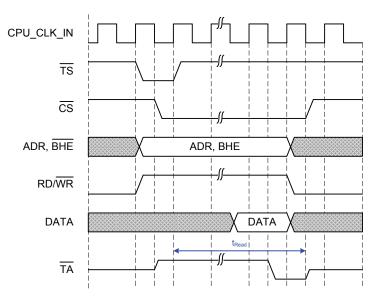

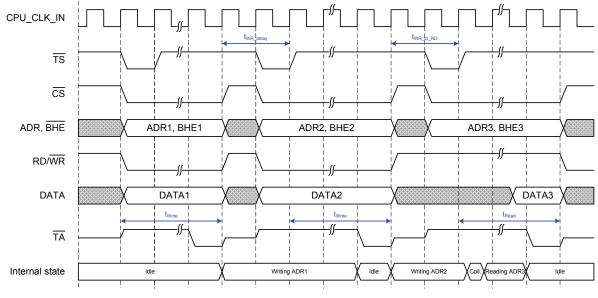

| Figure 10: Write access                                                  |    |

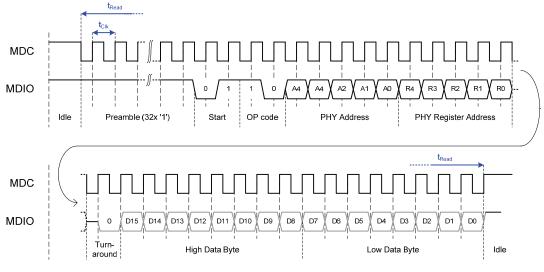

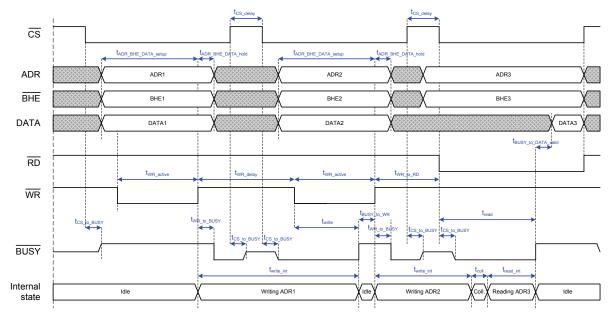

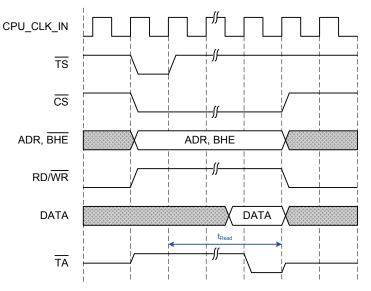

| Figure 11: Read access                                                   |    |

| Figure 12: Termination and Grounding Recommendation                      |    |

| Figure 13: RJ45 Connector                                                |    |

| Figure 14: M12 D-code Connector                                          |    |

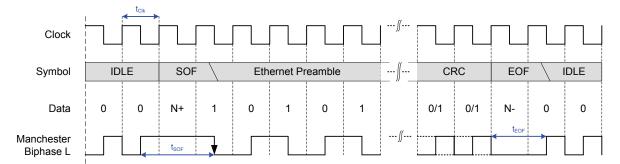

| Figure 15: Back-to-Back MII Connection (two ESCs)                        |    |

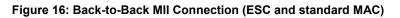

| Figure 16: Back-to-Back MII Connection (ESC and standard MAC)            |    |

| Figure 17: EBUS Interface Signals                                        |    |

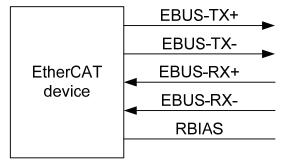

| Figure 18: EBUS Protocol                                                 |    |

| Figure 19: Example EtherCAT Network                                      |    |

| Figure 20: EBUS Connection                                               |    |

| Figure 21: FMMU Mapping Principle                                        |    |

| Figure 22: FMMU Mapping Example                                          | 39 |

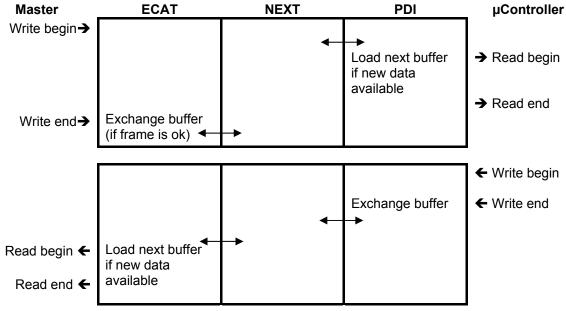

| Figure 23: SyncManager Buffer allocation                                 |    |

| Figure 24: SyncManager Buffered Mode Interaction                         |    |

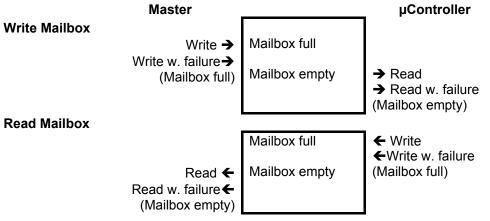

| Figure 25: SyncManager Mailbox Interaction                               |    |

| Figure 26: EtherCAT Mailbox Header (for all Types)                       |    |

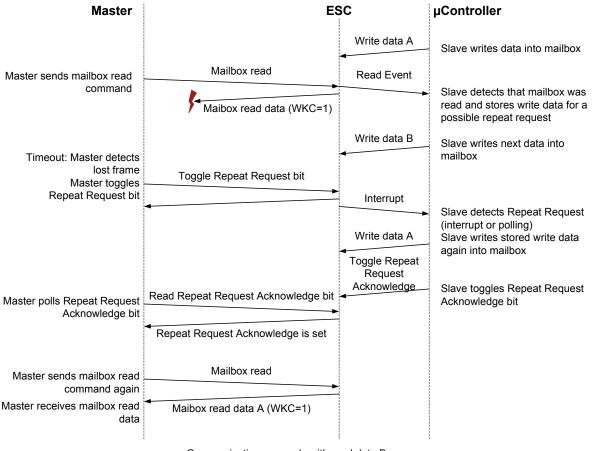

| Figure 27: Handling of Write/Read Toggle with Read Mailbox               |    |

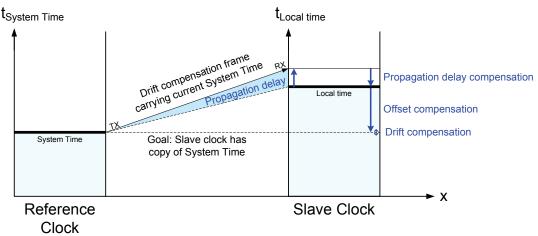

| Figure 28: Propagation Delay, Offset, and Drift Compensation             |    |

| Figure 29: Propagation Delay Calculation                                 |    |

| Figure 30: Distributed Clocks signals                                    |    |

| Figure 31: SyncSignal Generation Modes                                   |    |

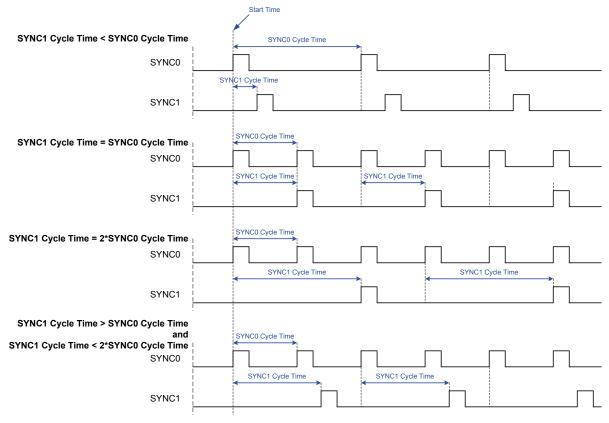

| Figure 32: SYNC0/1 Cycle Time Examples                                   |    |

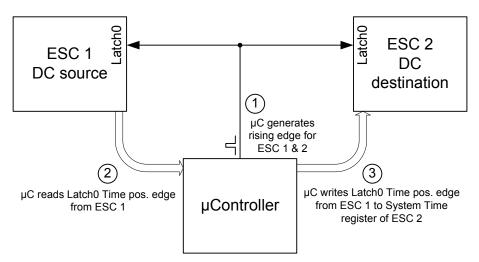

| Figure 33: System Time PDI Controlled with three steps                   |    |

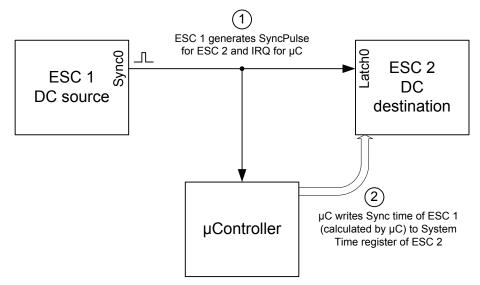

| Figure 34: System Time PDI Controlled with two steps                     | 63 |

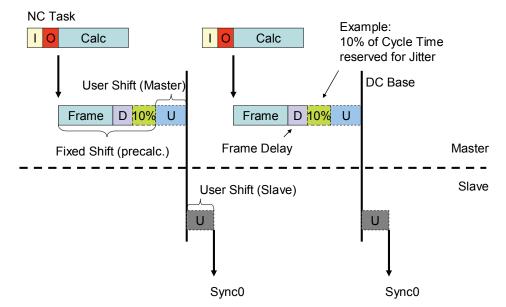

| Figure 35: DC Timing Signals in relation to Communication                |    |

| Figure 36: EtherCAT State Machine                                        |    |

| Figure 37: ESI EEPROM Layout                                             |    |

| Figure 38: I <sup>2</sup> C EEPROM signals                               |    |

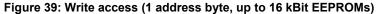

| Figure 39: Write access (1 address byte, up to 16 kBit EEPROMs)          |    |

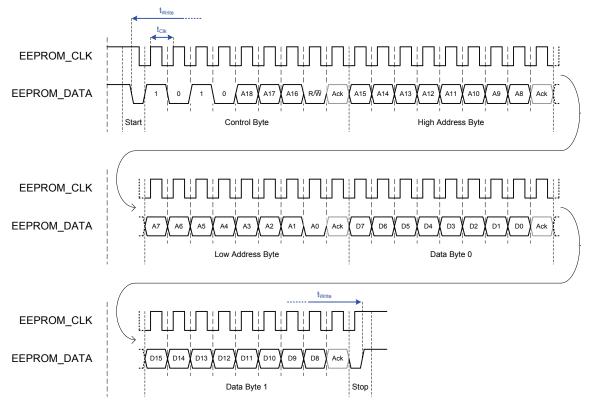

| Figure 40: Write access (2 address bytes, 32 kBit - 4 MBit EEPROMs)      |    |

| Figure 41: Read access (1 address byte, up to 16 kBit EEPROMs)           |    |

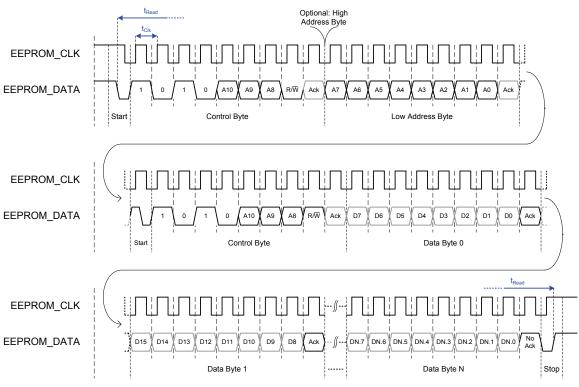

| Figure 42: PDI Interrupt Masking and interrupt signals                   |    |

| Figure 43: ECAT Interrupt Masking                                        | 82 |

## ABBREVIATIONS

| μC                           | Microcontroller                                                                                                                                                                          |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADR                          | Address                                                                                                                                                                                  |

| ADS                          | Automation Device Specification (Beckhoff)                                                                                                                                               |

| AL                           | Application Layer                                                                                                                                                                        |

| APRD<br>APWR<br>APRW<br>ARMW | Auto Increment Physical Read<br>Auto Increment Physical Write<br>Auto Increment Physical ReadWrite<br>Auto Increment Physical Read Multiple Write                                        |

| AoE                          | ADS over EtherCAT                                                                                                                                                                        |

| ASIC                         | Application Specific Integrated Chip                                                                                                                                                     |

| Auto Crossover               | Automatic detection of whether or not the send and receive lines are crossed.                                                                                                            |

| Auto Negotiation             | Automatic negotiation of transmission speeds between two stations.                                                                                                                       |

| Avalon®                      | On-chip bus for Altera <sup>®</sup> FPGAs                                                                                                                                                |

| Big Endian                   | Data format (also Motorola format). The more significant byte is transferred first when a word is transferred. However, for EtherCAT the least significant bit is the first on the wire. |

| BOOT                         | BOOT state of EtherCAT state machine                                                                                                                                                     |

| Boundary Clock               | A station that is synchronized by another station and then passes this information on.                                                                                                   |

| Bridge                       | A term for switches used in standards. Bridges are devices that pass on messages based on address information.                                                                           |

| Broadcast                    | An unacknowledged transmission to an unspecified number of receivers.                                                                                                                    |

| BRD<br>BWR<br>BRW            | Broadcast Read<br>Broadcast Write<br>Broadcast ReadWrite                                                                                                                                 |

| Cat                          | Category – classification for cables that is also used in Ethernet. Cat 5 is the minimum required category for EtherCAT. However, Cat 6 and Cat 7 cables are available.                  |

| CoE                          | CANopen over EtherCAT                                                                                                                                                                    |

| Communication<br>Stack       | A communication software package that is generally divided into successive layers, which is why it is referred to as a stack.                                                            |

| Confirmed                    | Means that the initiator of a service receives a response.                                                                                                                               |

| CRC                          | Cyclic Redundancy Check, used for FCS                                                                                                                                                    |

| Cut Through                  | Procedure for cutting directly through an Ethernet frame by a switch before the complete message is received.                                                                            |

| Cycle                        | Cycle in which data is to be exchanged in a system operating on a periodical basis.                                                                                                      |

| DC            | Distributed Clocks<br>Mechanism to synchronize EtherCAT slaves and master                                                                                             |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Delay         | Delays can be caused by run-times during transfer or internal delays of a network component.                                                                          |

| Dest Addr     | Destination address of a message (the destination can be an individual network station or a group (multicast).                                                        |

| DHCP          | Dynamic Host Configuration Protocol, used to assign IP addresses (and other important startup parameter in the Internet context).                                     |

| DL            | Data Link Layer, also known as Layer 2. EtherCAT uses the Data Link Layer of Ethernet, which is standardized as IEEE 802.3.                                           |

| DNS           | Domain Name Service, a protocol for domain name to IP addresses resolution.                                                                                           |

| EBUS          | Based on LVDS (Low Voltage Differential Signaling) standard specified in ANSI/TIA/EIA-644-1995                                                                        |

| ECAT          | EtherCAT                                                                                                                                                              |

| EEPROM        | Electrically Erasable Programmable Read Only Memory. Non-volatile memory used to store ESC configuration and device description. Connected to the ESI interface.      |

| EMC           | Electromagnetic Compatibility, describes the robustness of a device with regard to electrical interference from the environment.                                      |

| EMI           | Electromagnetic Interference                                                                                                                                          |

| Engineering   | Here: All applications required to configure and program a machine.                                                                                                   |

| EoE           | Ethernet over EtherCAT                                                                                                                                                |

| EOF           | End of Frame                                                                                                                                                          |

| ERR           | Error indicator for AL state                                                                                                                                          |

| Err(x)        | Physical Layer RX Error LED for debugging purposes                                                                                                                    |

| ESC           | EtherCAT Slave Controller                                                                                                                                             |

| ESI           | EtherCAT Slave Information, stored in ESI EEPROM (formerly known as SII)                                                                                              |

| ESM           | EtherCAT State Machine                                                                                                                                                |

| ETG           | EtherCAT Technology Group ( <u>http://www.ethercat.org</u> )                                                                                                          |

| EtherCAT      | Real-time Standard for Industrial Ethernet Control Automation Technology (Ethernet for Control Automation Technology)                                                 |

| EtherType     | Identification of an Ethernet frame with a 16-bit number assigned by IEEE. For example, IP uses EtherType 0x0800 (hexadecimal) and the EtherCAT protocol uses 0x88A4. |

| EPU           | EtherCAT Processing Unit. The logic core of an ESC containing e.g. registers, memory, and processing elements.                                                        |

| Fast Ethernet | Ethernet with a transmission speed of 100 Mbit/s.                                                                                                                     |

| FCC                          | Federal Communications Commission                                                                                                                                 |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FCS                          | Frame Check Sequence                                                                                                                                              |

| FIFO                         | First In First Out                                                                                                                                                |

| Firewall                     | Routers or other network component that acts as a gateway to the Internet and enables protection from unauthorized access.                                        |

| FMMU                         | Fieldbus Memory Management Unit                                                                                                                                   |

| FoE                          | File access over EtherCAT                                                                                                                                         |

| Follow Up                    | Message that follows Sync and indicates when the Sync frame was sent from the last node (defined in IEEE 1588).                                                   |

| FPGA                         | Field Programmable Gate Array                                                                                                                                     |

| FPRD<br>FPWR<br>FPRW<br>FRMW | Configured Address Physical Read<br>Configured Address Physical Write<br>Configured Address Physical ReadWrite<br>Configured Address Physical Read Multiple Write |

| Frame                        | See PDU                                                                                                                                                           |

| FTP                          | File Transfer Protocol                                                                                                                                            |

| Get                          | Access method used by a client to read data from a device.                                                                                                        |

| GND                          | Ground                                                                                                                                                            |

| GPI<br>GPO                   | General Purpose Input<br>General Purpose Output                                                                                                                   |

| HW                           | Hardware                                                                                                                                                          |

| I <sup>2</sup> C             | Inter-Integrated Circuit, serial bus used for ESI EEPROM connection                                                                                               |

| ICMP                         | Internet Control Message Protocol: Mechanisms for signaling IP errors.                                                                                            |

| IEC                          | International Electrotechnical Commission                                                                                                                         |

| IEEE                         | Institute of Electrical and Electronics Engineers                                                                                                                 |

| INIT                         | INIT state of EtherCAT state machine                                                                                                                              |

| Interval                     | Time span                                                                                                                                                         |

| IP                           | Internet Protocol: Ensures transfer of data on the Internet from end node to end node.<br>Intellectual Property                                                   |

| IRQ                          | Interrupt Request                                                                                                                                                 |

| ISO                          | International Standard Organization                                                                                                                               |

| ISO/OSI Model                | ISO Open Systems Interconnection Basic Reference Model (ISO 7498): describes the division of communication into 7 layers.                                         |

| IT                           | Information Technology: Devices and methods required for computer-aided information processing.                                                                   |

| LatchSignal           | Signal for Distributed Clocks time stamping                                                                                                                                                                                                                  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED                   | Light Emitting Diode, used as an indicator                                                                                                                                                                                                                   |

| Link/Act              | Link/Activity Indicator (LED)                                                                                                                                                                                                                                |

| Little Endian         | Data format (also Intel format). The less significant byte is transferred first when a word is transferred. With EtherCAT, the least significant bit is the first on the wire.                                                                               |

| LLDP                  | Lower Layer Discovery Protocol – provides the basis for topology discovery and configuration definition (see IEEE802.1ab)                                                                                                                                    |

| LRD<br>LWR<br>LRW     | Logical Read<br>Logical Write<br>Logical ReadWrite                                                                                                                                                                                                           |

| LVDS                  | Low Voltage Differential Signaling                                                                                                                                                                                                                           |

| M12                   | Connector used for industrial Ethernet                                                                                                                                                                                                                       |

| MAC                   | Media Access Control: Specifies station access to a communication medium.<br>With full duplex Ethernet, any station can send data at any time; the order of<br>access and the response to overload are defined at the network component<br>level (switches). |

| MAC Address           | Media Access Control Address: Also known as Ethernet address; used to identify an Ethernet node. The Ethernet address is 6 bytes long and is assigned by the IEEE.                                                                                           |

| Mandatory<br>Services | Mandatory services, parameters, objects, or attributes. These must be implemented by every station.                                                                                                                                                          |

| MBX                   | Mailbox                                                                                                                                                                                                                                                      |

| MDI                   | Media Dependant Interface:<br>Use of connector Pins and Signaling (PC side)                                                                                                                                                                                  |

| MDI-X                 | Media Dependant Interface (crossed):<br>Use of connector Pins and Signaling with crossed lines (Switch/hub side)                                                                                                                                             |

| MI                    | (PHY) Management Interface                                                                                                                                                                                                                                   |

| MII                   | Media Independent Interface: Standardized interface between the Ethernet MAC and PHY.                                                                                                                                                                        |

| Multicast             | Transmission to multiple destination stations with a frame – generally uses a special address.                                                                                                                                                               |

| NOP                   | No Operation                                                                                                                                                                                                                                                 |

| NVRAM                 | Non-volatile random access memory, e.g. EEPROM or Flash.                                                                                                                                                                                                     |

| Octet                 | Term from IEC 61158 – one octet comprises exactly 8 bits.                                                                                                                                                                                                    |

| OP                    | Operational state of EtherCAT state machine                                                                                                                                                                                                                  |

| OPB                   | On-Chip Peripheral Bus                                                                                                                                                                                                                                       |

| Optional Service      | Optional services can be fulfilled by a PROFINET station in addition to the mandatory services.                                                                                                                                                              |

| OSI              | Open System Interconnect                                                                                                                                                                                                                                          |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| OUI              | Organizationally Unique Identifier – are the first 3 Bytes of a Ethernet-Address, that will be assign to companies or organizations and can be used for protocol identifiers as well (e.g. LLDP)                                                                  |  |  |  |  |

| PDI              | Process Data Interface or Physical Device Interface: an interface that allows access to ESC from the process side.                                                                                                                                                |  |  |  |  |

| PDO              | Process Data Object                                                                                                                                                                                                                                               |  |  |  |  |

| PDU              | Protocol Data Unit: Contains protocol information (Src Addr, Dest Addr, Checksum and service parameter information) transferred from a protocol instance of transparent data to a subordinate level (the lower level contains the information being transferred). |  |  |  |  |

| PE               | Protection Earth                                                                                                                                                                                                                                                  |  |  |  |  |

| РНҮ              | Physical layer device that converts data from the Ethernet controller to electric or optical signals.                                                                                                                                                             |  |  |  |  |

| Ping             | Frame that verifies whether the partner device is still available.                                                                                                                                                                                                |  |  |  |  |

| PLB              | Processor Local Bus                                                                                                                                                                                                                                               |  |  |  |  |

| PLL              | Phase Locked Loop                                                                                                                                                                                                                                                 |  |  |  |  |

| PREOP            | Pre-Operational state of EtherCAT state machine                                                                                                                                                                                                                   |  |  |  |  |

| Priority Tagging | Priority field inserted in an Ethernet frame.                                                                                                                                                                                                                     |  |  |  |  |

| Protocol         | Rules for sequences – here, also the sequences (defined in state machines) and frame structures (described in encoding) of communication processes.                                                                                                               |  |  |  |  |

| Provider         | Device that sends data to other consumers in the form of a broadcast message.                                                                                                                                                                                     |  |  |  |  |

| PTP              | Precision Time Protocol in accordance with IEEE 1588: Precise time synchronization procedures.                                                                                                                                                                    |  |  |  |  |

| PTP Master       | Indicates time in a segment.                                                                                                                                                                                                                                      |  |  |  |  |

| PTP Slave        | Station synchronized by a PTP master.                                                                                                                                                                                                                             |  |  |  |  |

| Quad Cable       | Cable type in which the two cable pairs are twisted together. This strengthens the electromagnetic resistance.                                                                                                                                                    |  |  |  |  |

| RAM              | Random Access Memory. ESC have User RAM and Process Data RAM.                                                                                                                                                                                                     |  |  |  |  |

| Read             | Service enabling read access to an I/O device.                                                                                                                                                                                                                    |  |  |  |  |

| Real-Time        | Real-time capability of a system to perform a task within a specific time.                                                                                                                                                                                        |  |  |  |  |

| Request          | Call of a service in the sender/client.                                                                                                                                                                                                                           |  |  |  |  |

| Response         | Response to a service on the client side.                                                                                                                                                                                                                         |  |  |  |  |

| RJ45             | FCC Registered Jack, standard Ethernet connector (8P8C)                                                                                                                                                                                                           |  |  |  |  |

| RMII             | Reduced Media Independent Interface                                                                                                                                                                                                                               |  |  |  |  |

| Router           | Network component acting as a gateway based on the interpretation of the IP address.                                                                                                                                                                              |  |  |  |  |

| RSTP                                           | Rapid Spanning Tree Protocol: Prevents packet from looping infinitely between switches; RSTP is specified in IEEE 802.1 D (Edition 2004)                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RT                                             | Real-time. Name for a real-time protocol that can be run in Ethernet controllers without special support.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| RTC                                            | Real-time Clock chip of PCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| RT Frames                                      | EtherCAT Messages with EtherType 0x88A4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| RX                                             | Receive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| RXPDO                                          | Receive PDO, i.e. Process Data that will be received by ESC20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| RUN                                            | RUN indicator (LED) for application state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| SAFEOP                                         | Safe-Operational state of EtherCAT state machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Safety                                         | Safety function, implemented by an electric, electronic programmable fail-safe system that maintains the equipment in a safe state, even during certain critical external events.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Schedule                                       | Determines what should be transferred and when.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Services                                       | Interaction between two components to fulfill a specific task.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Set                                            | Access method used by a client to write data to a server.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

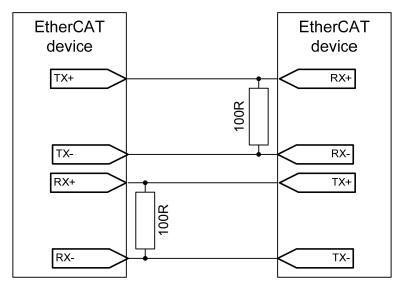

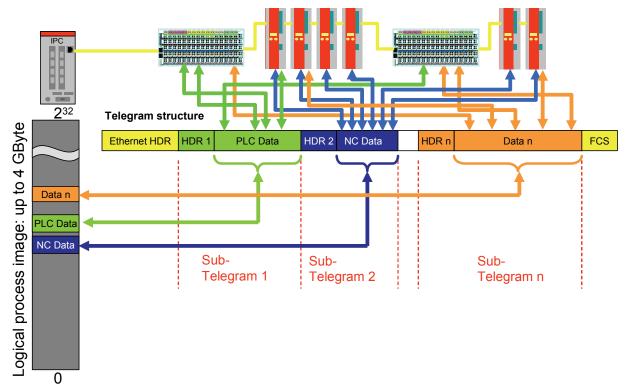

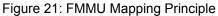

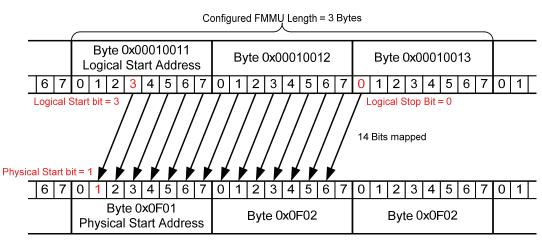

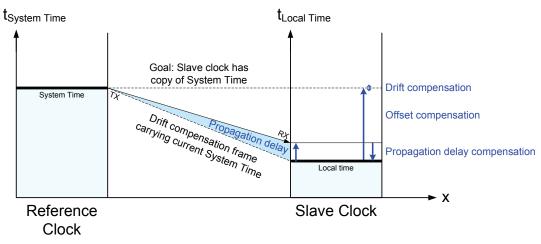

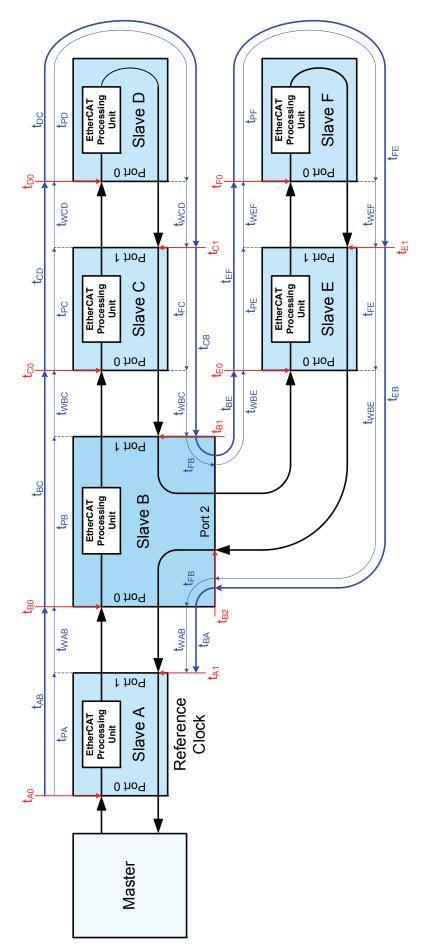

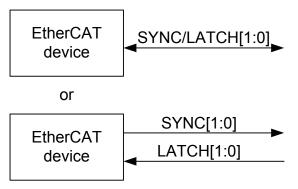

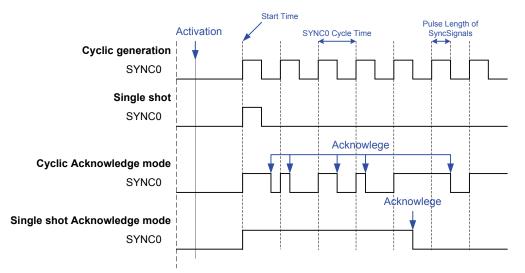

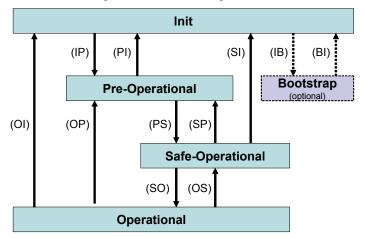

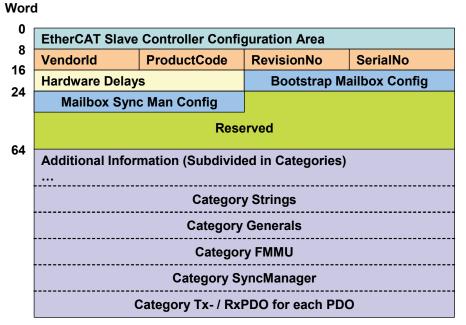

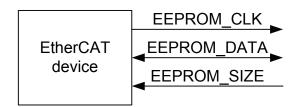

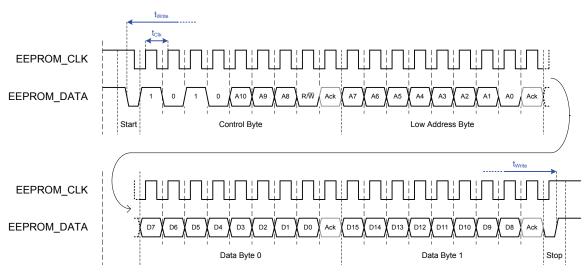

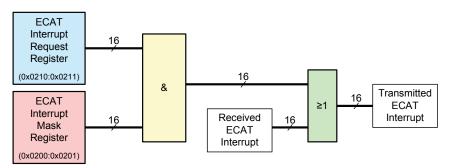

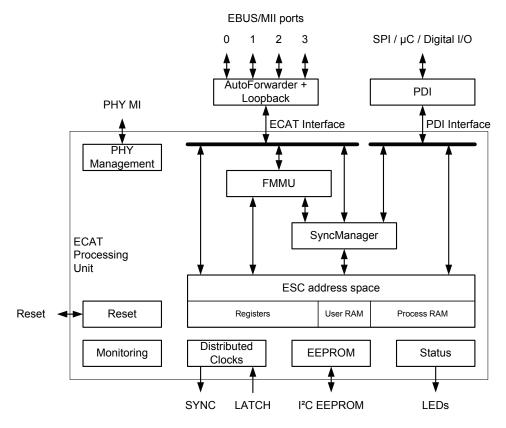

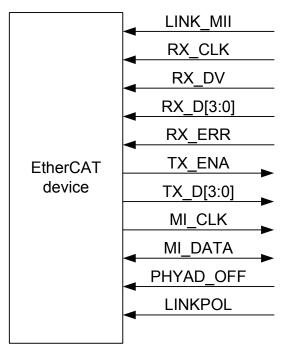

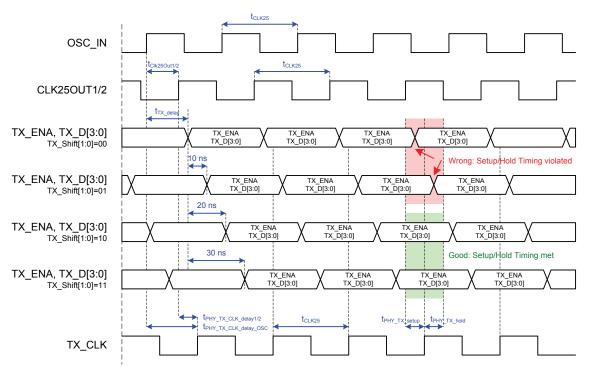

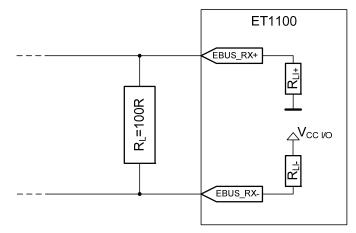

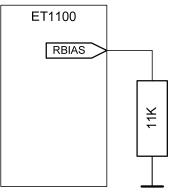

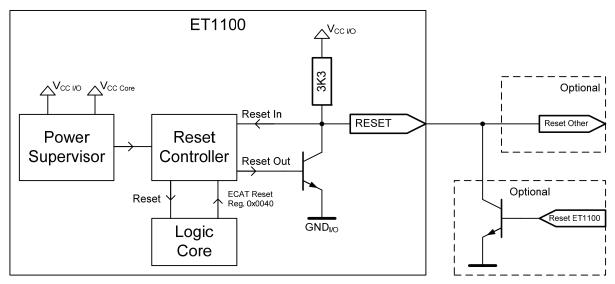

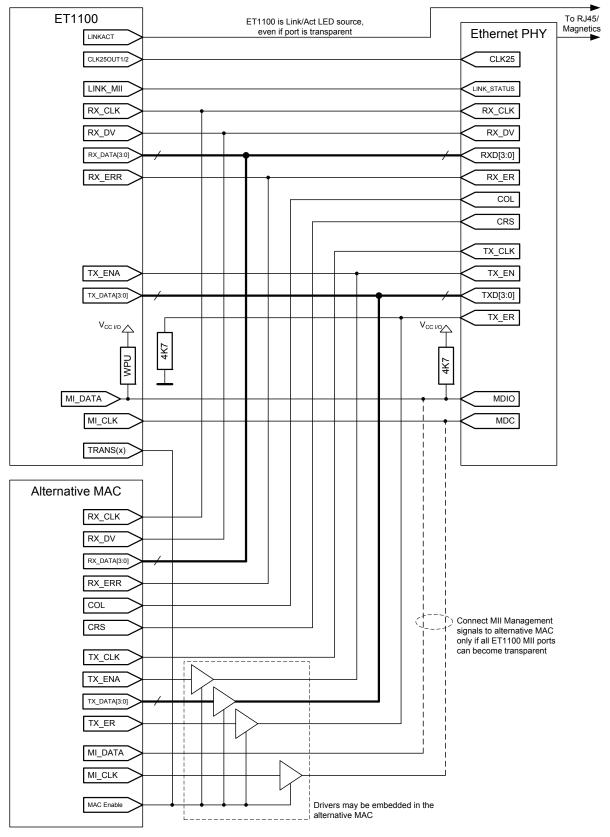

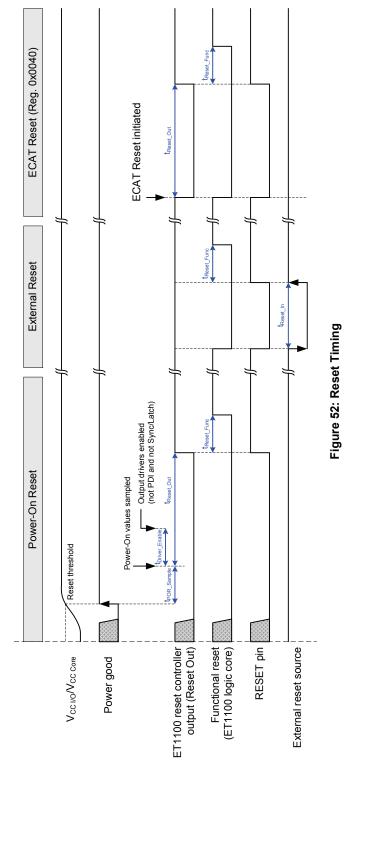

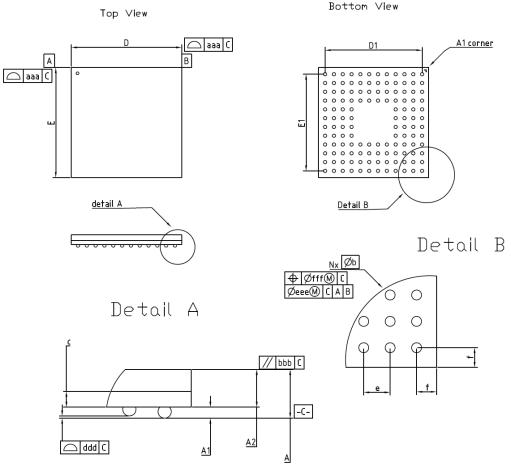

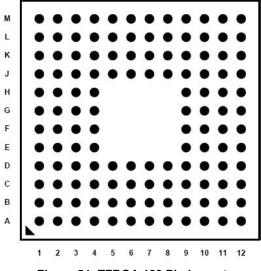

| SII                                            | Slave Information Interface, replaced by ESI interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |