**Data Sheet**

Features April 2006

- 512 channel x 512 channel non-blocking switch at 2.048 Mb/s, 4.096 Mb/s or 8.192 Mb/s operation

- Rate conversion between the ST-BUS inputs and ST-BUS outputs

- Per-stream ST-BUS input with data rate selection of 2.048 Mb/s, 4.096 Mb/s or 8.192 Mb/s

- Per-stream ST-BUS output with data rate selection of 2.048 Mb/s, 4.096 Mb/s or 8.192 Mb/s; the output data rate can be different than the input data rate

- Per-stream high impedance control output for every ST-BUS output with fractional bit advancement

- Per-stream input channel and input bit delay programming with fractional bit delay

- Per-stream output channel and output bit delay programming with fractional bit advancement

- Multiple frame pulse outputs and reference clock outputs

- Per-channel constant throughput delay

| Ordering Information        |                 |                       |  |  |  |  |

|-----------------------------|-----------------|-----------------------|--|--|--|--|

| ZL50012/QCC                 |                 | Trays                 |  |  |  |  |

| ZL50012/GDC                 | 144 Ball LBGA   | Trays                 |  |  |  |  |

| ZL50012QCG1                 | 160 Ball LQFP*  | Trays, Bake & Drypack |  |  |  |  |

| ZL50012GDG2                 | 144 Ball LBGA** | Trays, Bake & Drypack |  |  |  |  |

| *Pb Free Matte Tin          |                 |                       |  |  |  |  |

| **Pb Free Tin/Silver/Copper |                 |                       |  |  |  |  |

| -40°C to +85°C              |                 |                       |  |  |  |  |

- Per-channel high impedance output control

- Per-channel message mode

- Per-channel pseudo random bit sequence (PRBS) pattern generation and bit error detection

- Control interface compatible to Motorola nonmultiplexed CPUs

- Connection memory block programming capability

- IEEE-1149.1 (JTAG) test port

- 3.3V I/O with 5 V tolerant input

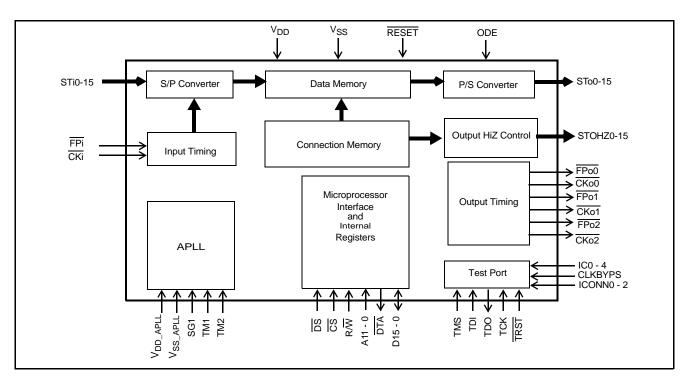

Figure 1 - ZL50012 Functional Block Diagram

#### **Applications**

- · Small and medium digital switching platforms

- Access Servers

- Time Division Multiplexers

- Computer Telephony Integration

- Digital Loop Carriers

### **Description**

The device has sixteen ST-BUS inputs (STi0-15) and sixteen ST-BUS outputs (STo0-15). It is a non-blocking digital switch with 512 64 kb/s channels and performs rate conversion between the ST-BUS inputs and ST-BUS outputs. The ST-BUS inputs accept serial input data streams with the data rate of 2.048 Mb/s, 4.096 Mb/s or 8.192 Mb/s on a per-stream basis. The ST-BUS outputs deliver serial output data streams with the data rate of 2.048 Mb/s, 4.096 Mb/s or 8.192 Mb/s on a per-stream basis. The device also provides sixteen high impedance control outputs (STOHZ 0-15) to support the use of external high impedance control buffers.

The ZL50012 has features that are programmable on per-stream or per-channel basis including message mode, input bit delay, output bit advancement, constant throughput delay and high impedance output control.

## **Table of Contents**

| Features                                                               | 1  |

|------------------------------------------------------------------------|----|

| Applications                                                           | 2  |

| Description                                                            | 2  |

| Changes Summary                                                        | 9  |

| 1.0 Device Overview                                                    | 16 |

| 2.0 Functional Description                                             | 16 |

| 2.1 ST-BUS Input Data Rate and Input Timing                            |    |

| 2.1.1 ST-BUS Input Operation Mode                                      |    |

| 2.1.2 Frame Pulse Input and Clock Input timing                         |    |

| 2.1.3 ST-BUS Input Timing                                              |    |

| 2.1.4 Improved Input Jitter Tolerance with Frame Boundary Determinator | 18 |

| 2.2 ST-Bus Output Data Rate and Output Timing                          | 19 |

| 2.2.1 ST-Bus Output Operation Mode                                     |    |

| 2.2.2 Frame Pulse Output and Clock Output Timing                       |    |

| 2.2.3 ST-BUS Output Timing                                             |    |

| 2.3 Serial Data Input Delay and Serial Data Output Offset              |    |

| 2.3.1 Input Channel Delay Programming                                  |    |

| 2.3.2 Input Bit Delay Programming                                      |    |

| 2.3.3 Fractional Input Bit Delay Programming                           |    |

| 2.3.4 Output Channel Delay Programming                                 |    |

| 2.3.5 Output Bit Delay Programming                                     |    |

| 2.3.6 Fractional Output Bit Advancement Programming                    |    |

| 2.3.7 External High Impedance Control, STOHZ 0 to 15                   |    |

| 2.4 Data Delay Through The Switching Paths                             |    |

| 2.5.1 Connection Memory Block Programming                              |    |

| 2.6 Bit Error Rate (BER) Test                                          |    |

| 2.7 Quadrant frame programming         2.8 Microprocessor Port         |    |

| ·                                                                      |    |

| 3.0 Device Reset and Initialization                                    |    |

| 4.0 JTAG Support                                                       |    |

| 4.1 Test Access Port (TAP)                                             |    |

| 4.2 Instruction Register                                               |    |

| 4.3 Test Data Register                                                 |    |

| 4.4 BSDL                                                               |    |

| 5.0 Register Address Mapping                                           |    |

| 6.0 Detail Register Description                                        | 37 |

# **List of Figures**

| Figure 1 - ZL50012 Functional Block Diagram                                                                            | 1 |

|------------------------------------------------------------------------------------------------------------------------|---|

| Figure 2 - 24 mm x 24 mm LQFP (JEDEC MS-026) Pinout Diagram                                                            | 0 |

| Figure 3 - 13 mm x 13 mm 144 Ball LBGA Pinout Diagram                                                                  |   |

| Figure 4 - Input Timing when (CKIN2 to CKIN0 bits = 010) in the Control Register                                       | 7 |

| Figure 5 - Input Timing when (CKIN2 to CKIN0 bits = 001) in the Control Register                                       | 7 |

| Figure 6 - Input Timing when (CKIN2 to CKIN0 bits = 000) in the Control Register                                       | 7 |

| Figure 7 - ST-BUS Input Timing for Various Input Data Rates                                                            | 8 |

| Figure 8 - FPo0 and CKo0 Output Timing when the CKFP0 bit = 0                                                          | 0 |

| Figure 9 - FPo0 and CKo0 Output Timing when the CKFP0 bit = 12                                                         |   |

| Figure 10 - FPo1 and CKo1 Output Timing when the CKFP1 bit = 0                                                         |   |

| Figure 11 - FPo1 and CKo1 Output Timing when the CKFP1 bit = 1                                                         | 1 |

| Figure 12 - FPo2 and CKo2 Output Timing when the CKFP2 bit = 0                                                         | 1 |

| Figure 13 - FPo2 and CKo2 Output Timing when the CKFP2 bit = 1                                                         | 1 |

| Figure 14 - ST-BUS Output Timing for Various Output Data Rates                                                         | 2 |

| Figure 15 - Input Channel Delay Timing Diagram                                                                         | 3 |

| Figure 16 - Input Bit Delay Timing Diagram24                                                                           |   |

| Figure 17 - Output Channel Delay Timing Diagram24                                                                      |   |

| Figure 18 - Output Bit Delay Timing Diagram                                                                            |   |

| Figure 19 - Fractional Output Bit Advancement Timing Diagram29                                                         |   |

| Figure 20 - Example: External High Impedance Control Timing                                                            | 6 |

| Figure 21 - Data Throughput Delay when input and output channel delay are disabled for Input Ch0 switched to           |   |

| Output Ch0                                                                                                             |   |

| Figure 22 - Data Throughput Delay when input channel delay is enabled and output channel delay is disabled for         |   |

| Input Ch0 switched to Output Ch0                                                                                       |   |

| Figure 23 - Data Throughput Delay when input channel delay is disabled and output channel delay is enabled for         |   |

| Input Ch0 switch to Output Ch0                                                                                         | Ö |

| Figure 24 - Data Throughput Delay when input and output channel delay are enabled for Input Ch0 switched to Output Ch0 | Ω |

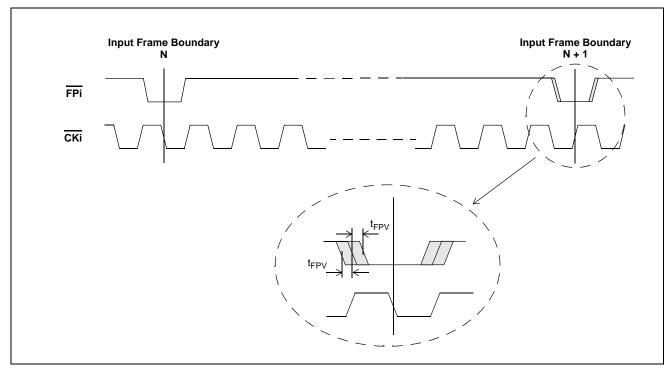

| Figure 25 - Frame Pulse Input and Clock Input Timing Diagram                                                           |   |

| Figure 26 - Frame Boundary Timing with Input Clock (cycle-to-cycle) Variation                                          |   |

| Figure 27 - Frame Boundary Timing with Input Frame Pulse (cycle-to-cycle) Variation                                    |   |

| Figure 28 - Input and Output Frame Boundary Offset                                                                     |   |

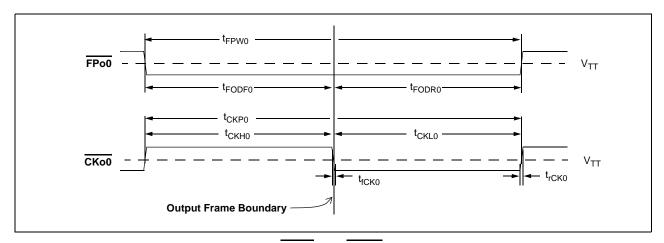

| Figure 29 - FPo0 and CKo0 Timing Diagram                                                                               |   |

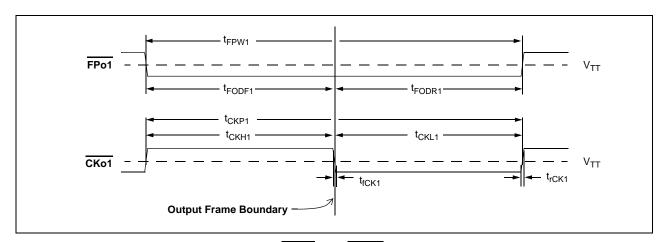

| Figure 30 - FPo1 and CKo1 Timing Diagram                                                                               |   |

| Figure 31 - FPo2 and CKo2 Timing Diagram                                                                               |   |

| Figure 32 - ST-BUS Inputs (STi0 - 15) Timing Diagram                                                                   |   |

| Figure 33 - ST-BUS Outputs (STo0 - 15) Timing Diagram                                                                  | _ |

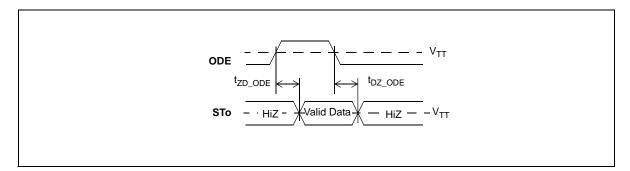

| Figure 34 - Serial Output and External Control                                                                         |   |

| Figure 35 - Output Driver Enable (ODE)                                                                                 |   |

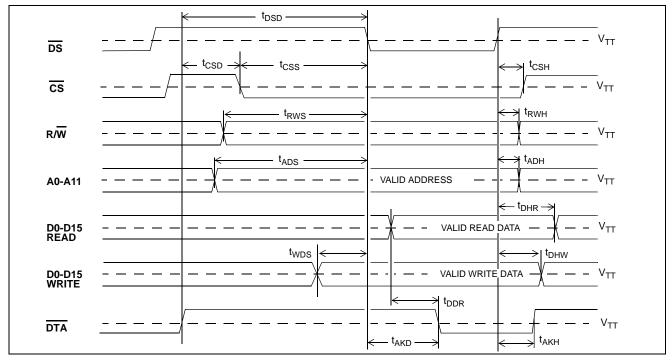

| Figure 36 - Motorola Non-Multiplexed Bus Timing                                                                        |   |

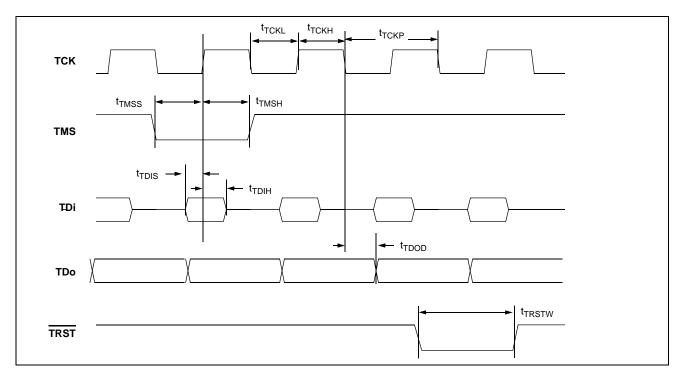

| Figure 37 - JTAG Test Port Timing Diagram                                                                              |   |

| Figure 38 - Reset Pin Timing Diagram                                                                                   |   |

| · .g                                                                                                                   | _ |

## **List of Tables**

| Table 1 - FPi and CKi Input Programming                                        | 16 |

|--------------------------------------------------------------------------------|----|

| Table 2 - FPo0 and CKo0 Output Programming                                     | 19 |

| Table 3 - FPo1 and CKo1 Output Programming                                     | 19 |

| Table 4 - FPo2 and CKo2 Output Programming                                     | 19 |

| Table 5 - Variable Range for Input Streams                                     | 27 |

| Table 6 - Variable Range for Output Streams                                    | 27 |

| Table 7 - Data Throughput Delay                                                | 27 |

| Table 8 - Connection Memory in Block Programming Mode                          | 30 |

| Table 9 - Definition of the Four Quadrant Frames                               | 32 |

| Table 10 - Quadrant Frame 0 LSB Replacement                                    | 32 |

| Table 11 - Quadrant Frame 1 LSB Replacement                                    | 32 |

| Table 12 - Quadrant Frame 2 LSB Replacement                                    | 32 |

| Table 13 - Quadrant Frame 3 LSB Replacement                                    | 32 |

| Table 14 - Address Map for Device Specific Registers                           | 35 |

| Table 15 - Control Register (CR) Bits                                          | 37 |

| Table 16 - Internal Mode Selection (IMS) Register Bits                         | 39 |

| Table 17 - BER Start Receiving Register (BSRR) Bits                            | 40 |

| Table 18 - BER Length Register (BLR) Bits                                      | 41 |

| Table 19 - BER Count Register (BCR) Bits                                       | 41 |

| Table 20 - Stream Input Control Register 0 to 7 (SICR0 to SICR7)               | 42 |

| Table 21 - Stream Input Control Register 8 to 15 (SICR8 to SICR15)             |    |

| Table 22 - Stream Input Delay Register 0 to 7 (SIDR0 to SIDR7)                 | 46 |

| Table 23 - Stream Input Delay Register 8 to 15 (SIDR8 to SIDR15)               |    |

| Table 24 - Stream Output Control Register 0 to 7 (SOCR0 to SOCR7)              |    |

| Table 25 - Stream Output Control Register 8 to 15 (SOCR8 to SOCR15)            |    |

| Table 26 - Stream Output Offset Register 0 to 7 (SOOR0 to SOOR7)               | 50 |

| Table 27 - Stream Output Offset Register 8 to 15 (SOOR8 to SOOR15)             |    |

| Table 28 - Address Map for Memory Locations (512 x 512 DX, MSB of address = 1) |    |

| Table 29 - Connection Memory Bit Assignment when the CMM bit = 0               | 53 |

| Table 30 - Connection Memory Bits Assignment when the CMM bit = 1              | 53 |

## **Changes Summary**

The following table captures the changes from the July 2004 issue.

| Page | Item                                                                      | Change                                                                                                                  |

|------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 18   | 2.1.4, "Improved Input Jitter Tolerance with Frame Boundary Determinator" | Added a new section to describe the improved input jitter tolerance with the frame boundary determinator.               |

| 37   | Table 15 -, "Control Register (CR) Bits" - bits , "FBDMODE" and , "FBDEN" | Renamed bit 15 from Unused to FBDMODE and<br>added description to clarify the frame boundary<br>determinator operation. |

|      |                                                                           | Clarified FBDEN description.                                                                                            |

ZL50012 Data Sheet

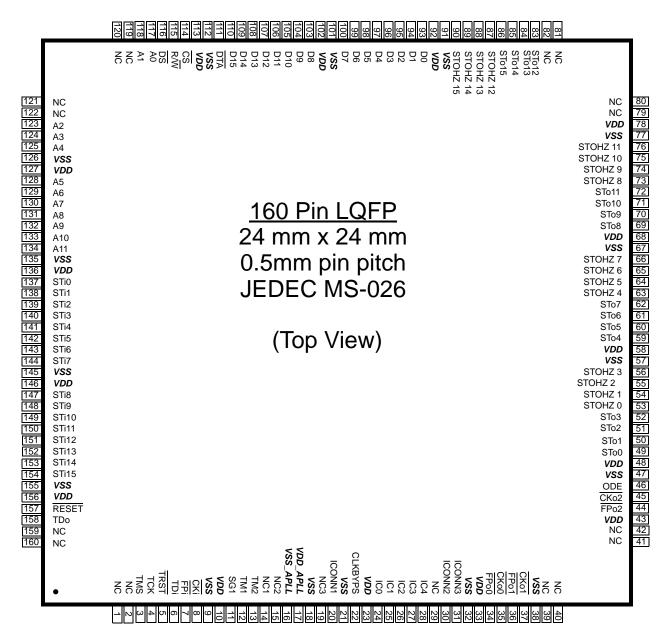

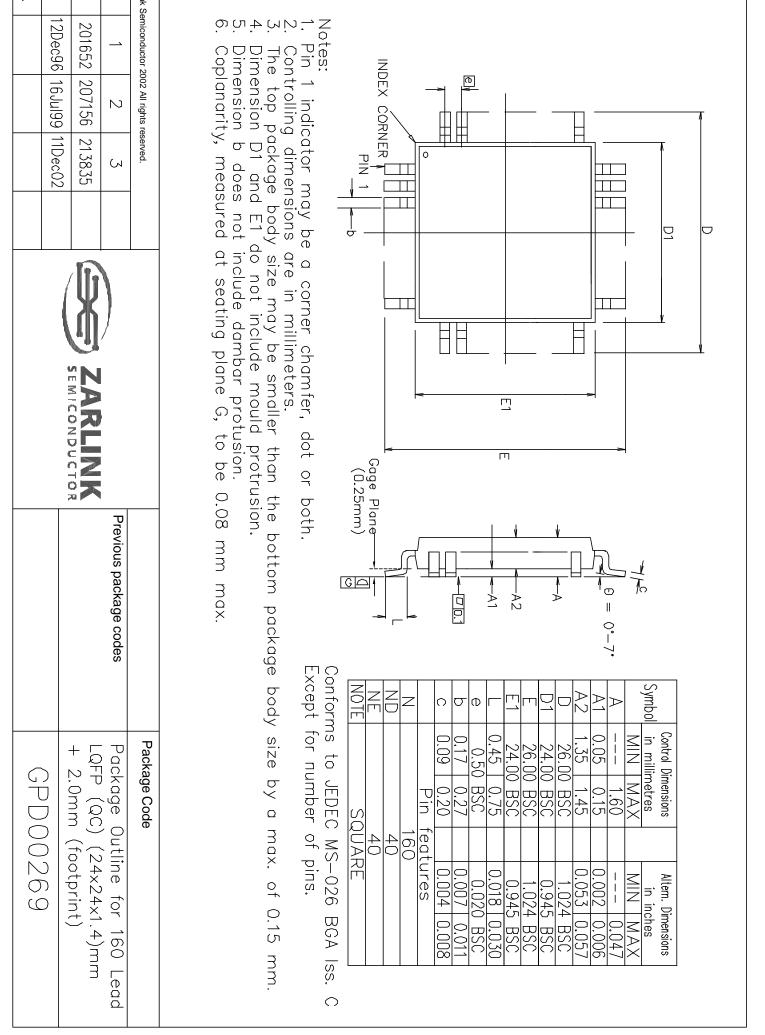

Figure 2 - 24 mm x 24 mm LQFP (JEDEC MS-026) Pinout Diagram

### PINOUT DIAGRAM: (as viewed through top of package)

A1 corner identified by metallized marking, mould indent, ink dot or right-angled corner

| \ | 1           | 2           | 3           | 4                 | 5   | 6   | 7           | 8            | 9    | 10   | 11    | 12    |

|---|-------------|-------------|-------------|-------------------|-----|-----|-------------|--------------|------|------|-------|-------|

| A | ODE         | FPo2        | FPo0        | ICONN<br>3        | IC1 | IC0 | ICONN<br>1  | NC3          | TM1  | CKi  | TDi   | TCK   |

| В | CKo2        | CKo1        | FPo1        | CK <sub>0</sub> 0 | IC3 | IC2 | CLK<br>BYPS | VDD_<br>APLL | SG1  | FPi  | TRST  | TMS   |

| С | STo2        | STo1        | STOHZ<br>0  | ICONN<br>2        | NC  | NC  | IC4         | NC2          | NC1  | TM2  | TDo   | STi15 |

| D | STo3        | STo0        | STOHZ<br>1  | VSS               | VDD | VDD | VDD         | VSS_<br>APLL | VSS  | STi8 | RESET | STi14 |

| E | STo5        | STo4        | STOHZ<br>3  | STOHZ<br>2        | VSS | VSS | VSS         | VSS          | VDD  | STi9 | STi13 | STi12 |

| F | STo6        | STo7        | STOHZ<br>4  | VDD               | VSS | VSS | VSS         | VSS          | VDD  | STi7 | STi10 | STi11 |

| G | STOHZ<br>6  | STOHZ<br>7  | STOHZ<br>5  | VDD               | VSS | VSS | VSS         | VSS          | STi1 | STi6 | STi5  | STi4  |

| Н | STo9        | STo10       | STo8        | VDD               | VSS | VSS | VSS         | VSS          | STi0 | DS   | STi2  | STi3  |

| J | STo11       | STOHZ<br>11 | STOHZ<br>8  | VSS               | D2  | VDD | VDD         | VDD          | A10  | A9   | A8    | A11   |

| К | STOHZ<br>9  | STOHZ<br>15 | STo15       | STOHZ<br>13       | D1  | D5  | CS          | D10          | D11  | A5   | A4    | A7    |

| L | STOHZ<br>10 | STo12       | STo13       | D3                | D15 | D4  | D7          | D12          | D14  | A2   | А3    | A6    |

| М | STo14       | STOHZ<br>12 | STOHZ<br>14 | D0                | DTA | D6  | D8          | D9           | D13  | A0   | A1    | R/W   |

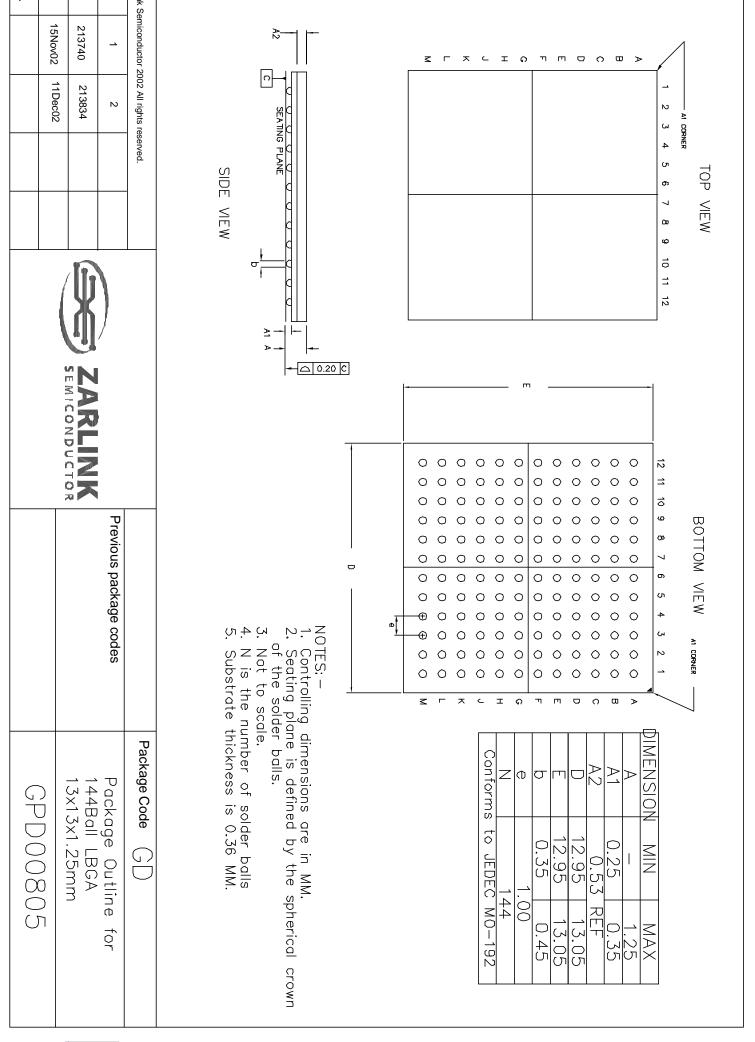

Figure 3 - 13 mm x 13 mm 144 Ball LBGA Pinout Diagram

## **Pin Description**

| ·                                                                                     |                                                                       |                       |                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LQFP Pin<br>Number                                                                    | LBGA Ball<br>Number                                                   | Name                  | Description                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 10, 23, 33,<br>43, 48, 58,<br>68, 78, 92,<br>102, 113,<br>127, 136,<br>146, 156       | D5, D6, D7<br>E9<br>F4, F9<br>G4<br>H4<br>J6, J7, J8                  | V <sub>DD</sub>       | Power Supply for the device: +3.3 V                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 9, 18, 21,<br>32, 38, 47,<br>57, 67, 77,<br>91, 101,<br>112, 126,<br>135, 145,<br>155 | D4, D9 E5, E6, E7, E8 F5, F6, F7, F8 G5, G6, G7, G8 H5, H6, H7, H8 J4 | V <sub>ss</sub> (GND) | Ground.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 3                                                                                     | B12                                                                   | TMS                   | <b>Test Mode Select (3.3 V Tolerant Input with internal pull-up):</b> JTAG signal that controls the state transitions of the TAP controller. This pin is pulled high by an internal pull-up resistor when it is not driven.                                                                                                                                                                                       |  |  |

| 4                                                                                     | A12                                                                   | TCK                   | <b>Test Clock (5 V Tolerant Input):</b> Provides the clock to the JTAG test logic.                                                                                                                                                                                                                                                                                                                                |  |  |

| 5                                                                                     | B11                                                                   | TRST                  | Test Reset (3.3 V Tolerant Input with internal pull-up): Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin should be pulsed low during power-up to ensure that the device is in the normal functional mode. When JTAG is not being used, this pin should be pulled low during normal operation.                                                            |  |  |

| 6                                                                                     | A11                                                                   | TDi                   | <b>Test Serial Data In (3.3 V Tolerant Input with internal pull-up):</b> JTAG serial test instructions and data are shifted in on this pin. This pin is pulled high by an internal pull-up resistor when it is not driven.                                                                                                                                                                                        |  |  |

| 7                                                                                     | B10                                                                   | FPi                   | ST-BUS Frame Pulse Input (5 V Tolerant Input): This pin accepts the frame pulse which stays low for 61 ns, 122 ns or 244 ns at the frame boundary. The frame pulse associating with the highest input data rate has to be applied to this pin. The frame pulse frequency is 8 kHz. The device also accepts positive frame pulse if the FPINP bit is high in the Internal Mode Selection register.                 |  |  |

| 8                                                                                     | A10                                                                   | СКі                   | ST-BUS Clock Input (5 V Tolerant Input): This pin accepts a 4.096 MHz, 8.192 MHz or 16.384 MHz clock. The input clock frequency has to be equal to or greater than twice of the highest input data rate. The clock falling edge defines the input frame boundary. The device also allows the clock rising edge to define the frame boundary by programming the CKINP bit in the Internal Mode Selection register. |  |  |

# **Pin Description (continued)**

| LQFP Pin<br>Number | LBGA Ball<br>Number   | Name                 | Description                                                                                                                                                                                                                                                                 |

|--------------------|-----------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11                 | В9                    | SG1                  | APLL Test Control (3.3 V Input with internal pull-down): For normal operation, this input MUST be low.                                                                                                                                                                      |

| 12                 | A9                    | TM1                  | APLL Test Pin 1: For normal operation, this input MUST be low.                                                                                                                                                                                                              |

| 13                 | C10                   | TM2                  | APLL Test Pin 2: For normal operation, this input MUST be low.                                                                                                                                                                                                              |

| 14, 15, 19         | C9, C8, A8            | NC1, NC2,<br>NC3     | No Connection: These pins MUST be left unconnected.                                                                                                                                                                                                                         |

| 16                 | D8                    | V <sub>ss_APLL</sub> | Ground for the APLL Circuit.                                                                                                                                                                                                                                                |

| 17                 | B8                    | V <sub>DD_APLL</sub> | Power Supply for the on-chip Analog Phase Lock Loop (APLL) Circuit: +3.3 V                                                                                                                                                                                                  |

| 20                 | A7                    | ICONN1               | Internal Connection: In normal mode, this pin must be low.                                                                                                                                                                                                                  |

| 22                 | В7                    | CLKBYPS              | <b>Test Clock Input:</b> For device testing only, in normal operation, this input MUST be low.                                                                                                                                                                              |

| 24 - 28            | A6, A5, B6,<br>B5, C7 | IC0 - 4              | Internal connection (3.3 V Tolerant Inputs with internal pull-down): In normal mode, these pins must be low.                                                                                                                                                                |

| 30, 31             | C4, A4                | ICONN2 - 3           | Internal Connection: In normal mode, these pins must be low.                                                                                                                                                                                                                |

| 34                 | А3                    | FPo0                 | ST-BUS Frame Pulse Output 0 (5 V Tolerance Three-state Output): ST-BUS frame pulse output which stays low for 244 ns or 122 ns at the output frame boundary. Its frequency is 8 KHz. The polarity of this signal can be changed using the Internal Mode Selection register. |

| 35                 | B4                    | CKo0                 | ST-BUS Clock Output 0 (5 V Tolerant Three-state Output): A 4.094 MHz or 8.192 MHz clock output. The clock falling edge defines the output frame boundary. The polarity of this signal can be changed using the Internal Mode Selection register.                            |

| 36                 | В3                    | FPo1                 | ST-BUS Frame Pulse Output 1 (5 V Tolerant Three-state Output): ST-BUS frame pulse output which stays low for 61 ns or 122 ns at the output frame boundary. Its frequency is 8 KHz. The polarity of this signal can be changed using the Internal Mode Selection register.   |

| 37                 | B2                    | CKo1                 | ST-BUS Clock Output 1 (5 V Tolerant Three-state Output): A 16.384 MHz or 8.192 MHz clock output. The clock falling edge defines the output frame boundary. The polarity of this signal can be changed using the Internal Mode Selection register.                           |

# **Pin Description (continued)**

| LQFP Pin<br>Number                            | LBGA Ball<br>Number                                                        | Name                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44                                            | A2                                                                         | FPo2                                                              | ST-BUS Frame Pulse Output 2 (5V Tolerant High Speed Three-state Output): ST-BUS frame pulse output which stays low for 30 ns or 61 ns at the frame boundary. Its frequency is 8 KHz. The polarity of this signal can be changed using the Internal Mode Selection register.                                                                                                                                                                                                                                        |

| 45                                            | B1                                                                         | CKo2                                                              | ST-BUS Clock Output 2 (5 V Tolerant High Speed Three-state Output): A 32.768 MHz or 16.384 MHz clock output. The clock falling edge defines the output frame boundary. The polarity of this signal can be changed using the Internal Mode Selection register.                                                                                                                                                                                                                                                      |

| 46                                            | A1                                                                         | ODE                                                               | Output Drive Enable (5 V Tolerant Input): This is the asynchronously output enable control for the STo0 - 15 and the output driven high control for the STOHZ 0 - 15 serial outputs. When it is high, the STo0 - 15 and STOHZ 0 - 15 are enabled. When it is low, the STo0 - 15 are in the high impedance state and the STOHZ 0 - 15 are driven high.                                                                                                                                                              |

| 49 - 52<br>59 - 62<br>69 - 72<br>83 - 86      | D2, C2, C1, D1<br>E2, E1, F1, F2<br>H3, H1, H2, J1<br>L2, L3, M1, K3       | STo0 - 3<br>STo4 - 7<br>STo8 - 11<br>STo12 - 15                   | Serial Output Streams 0 to 15 (5 V Tolerant Three-state Outputs): The data rate of these output streams can be selected independently using the stream control output registers. In the 2.048 Mb/s mode, these pins have serial TDM data streams at 2.048 Mb/s with 32 channels per stream. In the 4.096 Mb/s mode, these pins have serial TDM data streams at 4.096 Mb/s with 64 channels per stream. In the 8.192 Mb/s mode, these pins have serial TDM data streams at 8.192 Mb/s with 128 channels per stream. |

| 53 - 56<br>63 - 66<br>73 - 76<br>87 - 90      | C3, D3, E4, E3<br>F3, G3, G1,<br>G2<br>J3, K1, L1, J2<br>M2, K4, M3,<br>K2 | STOHZ 0 - 3<br>STOHZ 4 - 7<br>STOHZ 8 -<br>11<br>STOHZ 12 -<br>15 | Serial Output Streams High Impedance Control 0 to 15 (5 V Tolerant Three-state Outputs): These pins are used to enable (or disable) external three-state buffers. When a output channel is in the high impedance state, the STOHZ drives high for the duration of the corresponding output channel. When the STo channel is active, the STOHZ drives low for the duration of the corresponding output channel.                                                                                                     |

| 93 - 96<br>97 - 100<br>103 - 106<br>107 - 110 | M4, K5, J5, L4<br>L6, K6, M6, L7<br>M7, M8, K8,<br>K9<br>L8, M9, L9, L5    | D0 - D3<br>D4 - D7<br>D8 - D11<br>D12 - D15                       | Data Bus 0 - 15 (5 V Tolerant I/Os): These pins form the 16-bit data bus of the microprocessor port.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 111                                           | M5                                                                         | DTA                                                               | Data Transfer Acknowledgment (5 V Tolerant Three-state Output): This active low output indicates that a data bus transfer is complete. A pull-up resistor is required to hold this pin at HIGH level.                                                                                                                                                                                                                                                                                                              |

| 114                                           | K7                                                                         | <u>cs</u>                                                         | Chip Select (5 V Tolerant Input): Active low input used by the microprocessor to enable the microprocessor port access.                                                                                                                                                                                                                                                                                                                                                                                            |

# **Pin Description (continued)**

| LQFP Pin<br>Number                                                       | LBGA Ball<br>Number                                                                    | Name                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 115                                                                      | M12                                                                                    | R/W                                                                      | Read/Write (5 V Tolerant Input): This input controls the direction of the data bus lines (D0-D15) during a microprocessor access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 116                                                                      | H10                                                                                    | DS                                                                       | <b>Data Strobe (5 V Tolerant Input):</b> This active low input works in conjunction with $\overline{\text{CS}}$ to enable the microprocessor port read and write operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 117, 118<br>123 - 125<br>128 - 130<br>131 - 134                          | M10, M11<br>L10, L11, K11<br>K10, L12, K12<br>J11, J10, J9,<br>J12                     | A0 - A1<br>A2 - A4<br>A5 - A7<br>A8 - A11                                | Address 0 - 11 (5 V Tolerant Inputs): These pins form the 12-bit address bus to the internal memories and registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 137 - 139<br>140 - 142<br>143, 144<br>147 - 149<br>150 - 152<br>153, 154 | H9, G9, H11<br>H12, G12, G11<br>G10, F10<br>D10, E10, F11<br>F12, E12, E11<br>D12, C12 | STi0 - 2<br>STi3 - 5<br>STi6 - 7<br>STi8 - 10<br>STi11- 13<br>STi14 - 15 | Serial Input Streams 0 to 15 (5 V Tolerant Inputs): The data rate of these input streams can be selected independently using the stream input control registers. In the 2.048 Mb/s mode, these pins accept serial TDM data streams at 2.048 Mb/s with 32 channels per stream. In the 4.096 Mb/s mode, these pins accept serial TDM data streams at 4.096 Mb/s with 64 channels per stream. In the 8.192 Mb/s mode, these pins accept serial TDM data streams at 8.192 Mb/s with 128 channels per stream.  Unused serial input pins are required to connect to either Vdd or ground, through an external pull-up resistors or external pull-down resistor. |  |

| 157                                                                      | D11                                                                                    | RESET                                                                    | Device Reset (5 V Tolerant Input): This input (active LOW) puts the device in its reset state that disables the STo0 - 15 drivers and drives the STOHZ 0 - 15 outputs to high. It also clears the device registers and internal counters. To ensure proper reset action, the reset pin must be low for longer than 1 ms. Upon releasing the reset signal to the device, the first microprocessor access can take place after 600 μs due to the time required to stabilize the APLL block from the power down state.                                                                                                                                       |  |

| 158                                                                      | C11                                                                                    | TDo                                                                      | Test Serial Data Out (3 V Tolerant Three-state Output): JTAG serial data is output on this pin on the falling edge of TCK. This pin is held in high impedance state when JTAG is not enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 1, 2, 29,<br>39 - 42,<br>79 - 82,<br>119 - 122,<br>159, 160              | C5, C6                                                                                 | NC                                                                       | No Connection Pins. These pins are not connected to the device internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

#### 1.0 Device Overview

The device uses the ST-BUS input frame pulse and the ST-BUS input clock to define the input frame boundary and timing for the ST-BUS input streams with various data rates (2.048 Mb/s, 4.096 Mb/s and/or 8.192 Mb/s). The output frame boundary is defined by the output frame pulses and the output clock timing for the ST-BUS output streams with various data rates (2.048 Mb/s, 4.096 Mb/s and/or 8.192 Mb/s).

By using Zarlink's message mode capability, microprocessor data can be broadcast to the data output streams on a per channel basis. This feature is useful for transferring control and status information for external circuits or other ST-BUS devices.

A non-multiplexed microprocessor port allows users to program the device with various operating modes and switching configurations. Users can use the microprocessor port to perform register read/write, connection memory read/write and data memory read operations. The microprocessor port has a 12-bit address bus, a 16-bit data bus and four control signals.

The device also supports the mandatory requirements of the IEEE-1149.1 (JTAG) standard via the test port.

### 2.0 Functional Description

A functional block diagram of the ZL50012 is shown in Figure 1 on page 1.

#### 2.1 ST-BUS Input Data Rate and Input Timing

The device has sixteen ST-BUS serial data inputs. Any of the sixteen inputs can be programmed to accept different data rates, 2.048 Mb/s, 4.096 Mb/s or 8.192 Mb/s.

#### 2.1.1 ST-BUS Input Operation Mode

Any ST-BUS input can be programmed to accept the 2.048 Mb/s, 4.096 Mb/s or 8.192 Mb/s data using Bit 0 to 2 in the stream input control registers, SICR0 to SICR15 as shown in Table 20 on page 42 and Table 21 on page 44.

The maximum number of input channels is 512 channels. External pull-up or pull-down resistors are required for any unused ST-BUS inputs.

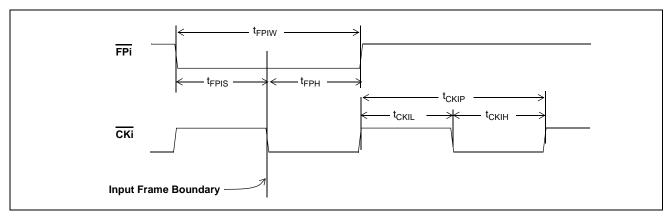

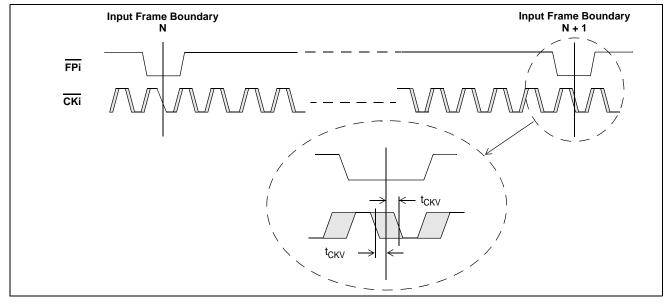

#### 2.1.2 Frame Pulse Input and Clock Input timing

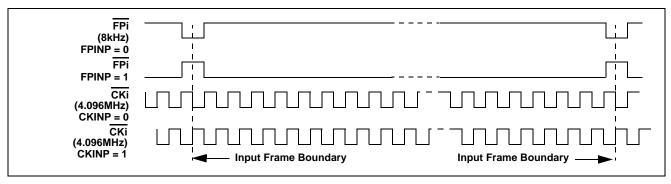

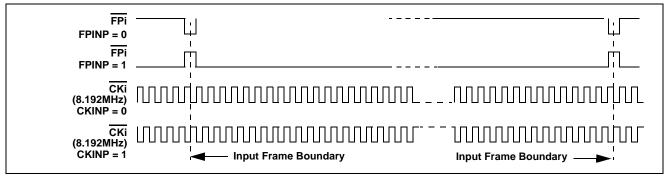

The frame pulse input  $\overline{FPi}$  accepts the frame pulse used for the **highest** input data rate. The frame pulse is an 8 kHz input signal which stays low for 244 ns, 122 ns or 61 ns for the input data rate of 2.048 Mb/s, 4.096 Mb/s or 8.192 Mb/s respectively. The frequency of  $\overline{CKi}$  must be twice the highest data rate. For example, if users present the ZL50012 with 2.048 Mb/s and 8.192 Mb/s input data, the device should be programmed to accept the input clock of 16.384 MHz and the frame pulse which stays low for 61 ns.

Users have to program the CKIN2 - 0 bits in the Control Register (CR), for the width of the frame pulse low cycle and the frequency of the input clock. See Table 1 for the programming of the CKIN0, CKIN1 and CKIN2 bits in the Control Register.

| CKIN2 - 0 bits | FPi Low Cycle | CKi        | Highest Input Data Rate |

|----------------|---------------|------------|-------------------------|

| 000            | 61 ns         | 16.384 MHz | 8.192 Mb/s              |

| 001            | 122 ns        | 8.192 MHz  | 4.096 Mb/s              |

| 010            | 244 ns        | 4.096 MHz  | 2.048 Mb/s              |

| 011 - 111      | Rese          |            |                         |

Table 1 - FPi and CKi Input Programming

ZL50012 Data Sheet

The device also accepts positive or negative input frame pulse and ST-BUS input clock formats via the programming of the FPINP and CKINP bits in the Internal Mode Selection (IMS) register. By default, the device accepts the negative input clock format.

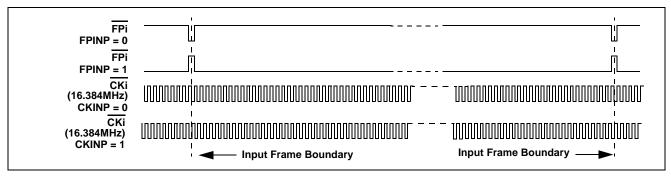

Figure 4, Figure 5 and Figure 6 describe the usage of CKIN2 - 0, FPINP and CKINP in the Internal Mode Selection (IMS) register:

Figure 4 - Input Timing when (CKIN2 to CKIN0 bits = 010) in the Control Register

Figure 5 - Input Timing when (CKIN2 to CKIN0 bits = 001) in the Control Register

Figure 6 - Input Timing when (CKIN2 to CKIN0 bits = 000) in the Control Register

#### 2.1.3 ST-BUS Input Timing

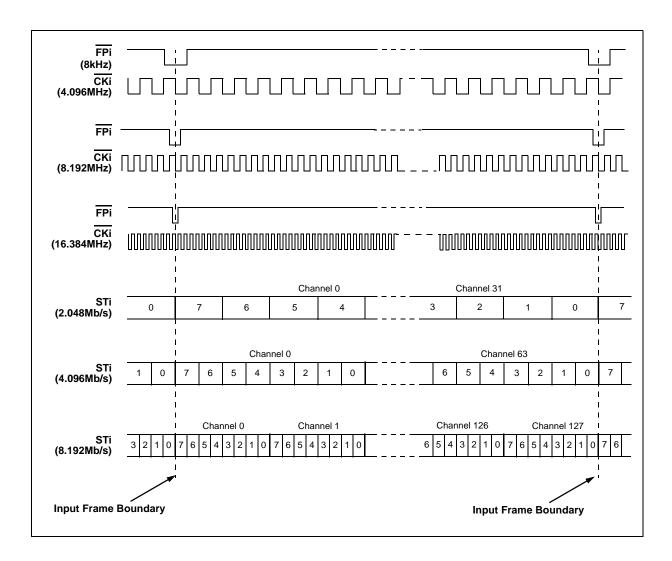

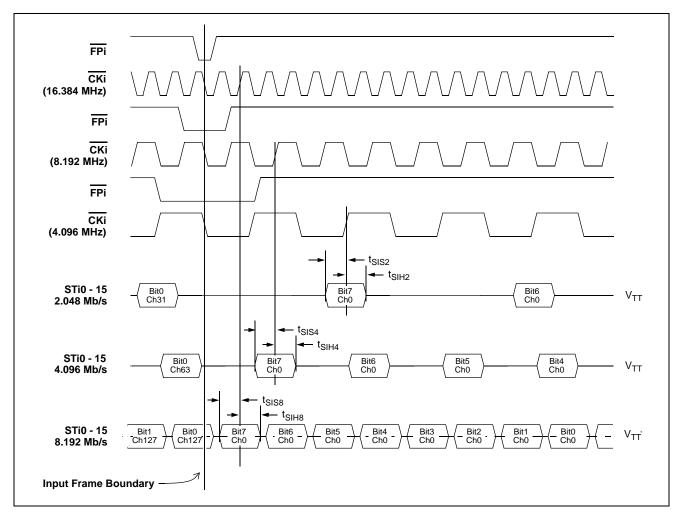

When the negative input frame pulse and negative input clock formats are used, the input frame boundary is defined by the falling edge of the CKi input clock while the FPi is low. When the input data rate is 2.048 Mb/s, 4.096 Mb/s or 8.192 Mb/s, there are 32, 64 or 128 channels per every ST-BUS frame respectively. Figure 7 shows the details:

Figure 7 - ST-BUS Input Timing for Various Input Data Rates

#### 2.1.4 Improved Input Jitter Tolerance with Frame Boundary Determinator

The ZL50012 has a Frame Boundary Determinator (FBD) allowing substantial increase of the CKi input clock jitter tolerance. The FBD circuit is enabled by setting the Control Register bits FBDEN and FBDMODE to HIGH. By default the FBD is disabled. Both the FBDEN and FBDMODE bits should be set HIGH during normal operation. The device can have 20 ns of input clock jitter tolerance (on CKi and FPi) when the FBD is fully enabled.

#### 2.2 ST-Bus Output Data Rate and Output Timing

The device has sixteen ST-BUS serial data outputs. Any of the sixteen outputs can be programmed to deliver different data rates at 2.048 Mb/s, 4.096 Mb/s or 8.192 Mb/s.

#### 2.2.1 ST-Bus Output Operation Mode

Any ST-Bus output can be programmed to deliver the data at 2.048 Mb/s, 4.096 Mb/s or 8.192 Mb/s mode using Bit 0 to 2 in the Stream Output Control Register, SOCR0 to SOCR15 as shown in Table 24 on page 48 and Table 25 on page 49.

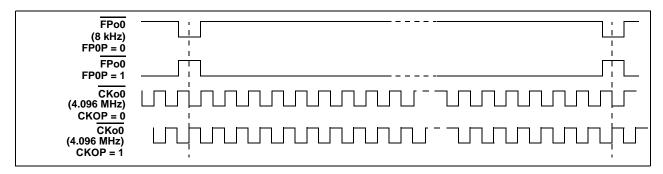

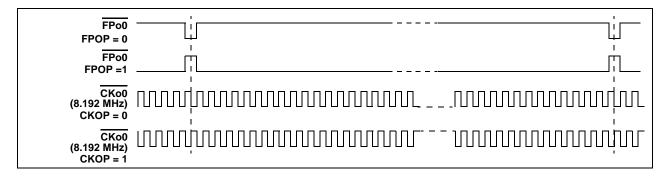

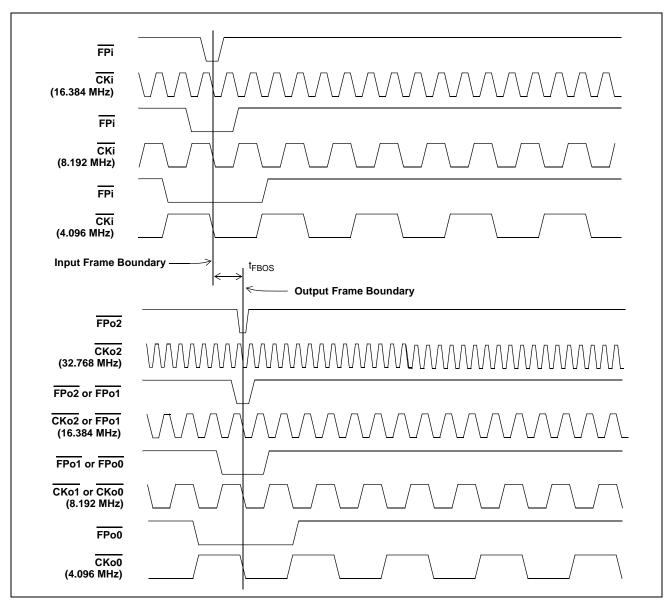

#### 2.2.2 Frame Pulse Output and Clock Output Timing

The device offers three frame pulse outputs, FPo0, FPo1 and FPo2. All output frame pulses are 8kHz output signals. By default, output frame boundary is defined by the falling edge of the CKo0, CKo1 or CKo2 output clocks while the FPo0, FPo1 or FPo2 output frame pulse goes low respectively.

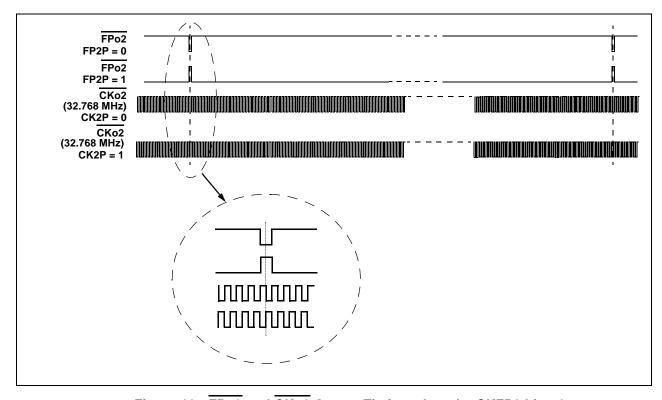

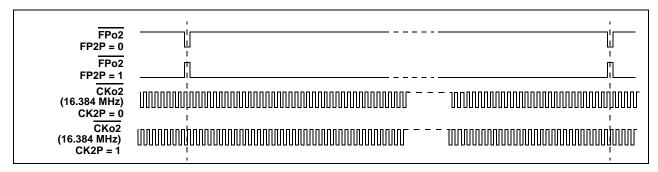

In addition to the default settings, users can also select different output frame pulse low cycles and output clock frequencies by programming the CKFP0, CKFP1 and CKFP2 bits in the Control Register. See Table 2, Table 3 and Table 4 for the bit usage in the Control Register:

| CKFP0 | KFP0 FP00 CK00 |           |

|-------|----------------|-----------|

| 0     | 244 ns         | 4.096 MHz |

| 1     | 122 ns         | 8.192 MHz |

Table 2 - FPo0 and CKo0 Output Programming

| CKFP1 | FPo1   | CKo1       |

|-------|--------|------------|

| 0     | 61 ns  | 16.384 MHz |

| 1     | 122 ns | 8.192 MHz  |

Table 3 - FPo1 and CKo1 Output Programming

| CKFP2 | FPo2  | CKo2       |

|-------|-------|------------|

| 0     | 30 ns | 32.768 MHz |

| 1     | 61 ns | 16.384 MHz |

Table 4 - FPo2 and CKo2 Output Programming

ZL50012 Data Sheet

The device also delivers positive or negative output frame pulse and ST-BUS output clock formats via the programming of the FP0P, FP1P, FP2P, CK0P, CK1P and CK2P bits in the Internal Mode Selection (IMS) register. By default, the device delivers the negative output frame pulse and negative output clock formats.

Figure 8 to Figure 13 describe the usage of the CKFP0, CKFP1, CKFP2, FP0P, FP1P, FP2P, CK0P, CK1P and CK2P in the Control Register and Internal Mode Selection Register:

Figure 8 - FPo0 and CKo0 Output Timing when the CKFP0 bit = 0

Figure 9 - FPo0 and CKo0 Output Timing when the CKFP0 bit = 1

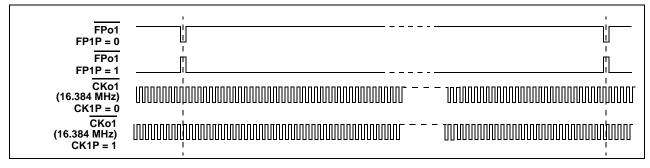

Figure 10 -  $\overline{\text{FPo1}}$  and  $\overline{\text{CKo1}}$  Output Timing when the CKFP1 bit = 0

Figure 11 - FPo1 and CKo1 Output Timing when the CKFP1 bit = 1

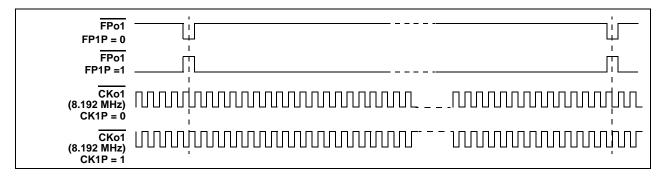

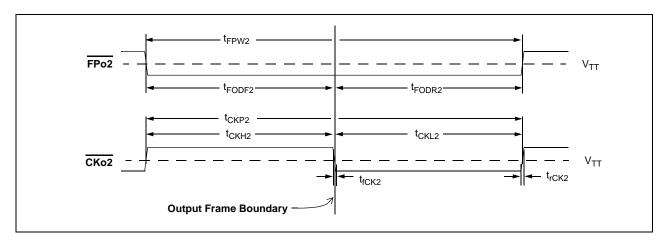

Figure 12 -  $\overline{FPo2}$  and  $\overline{CKo2}$  Output Timing when the CKFP2 bit = 0

Figure 13 - FPo2 and CKo2 Output Timing when the CKFP2 bit = 1

#### 2.2.3 ST-BUS Output Timing

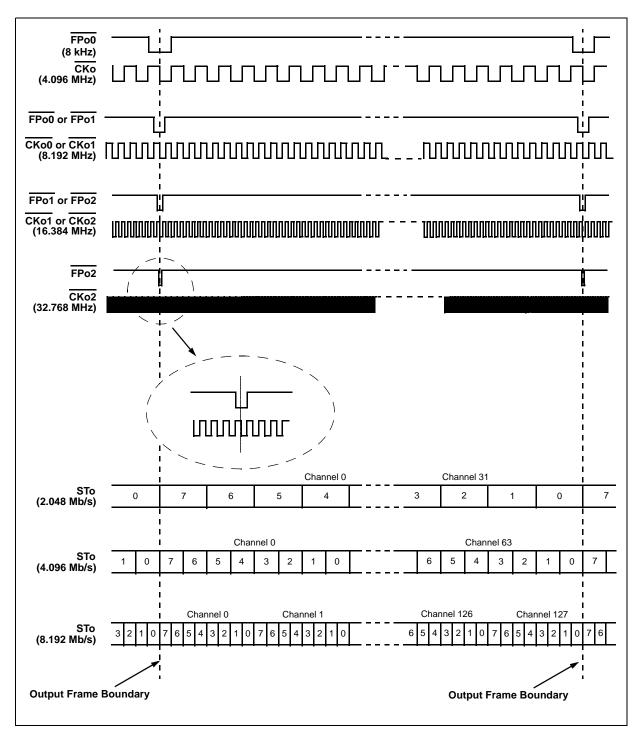

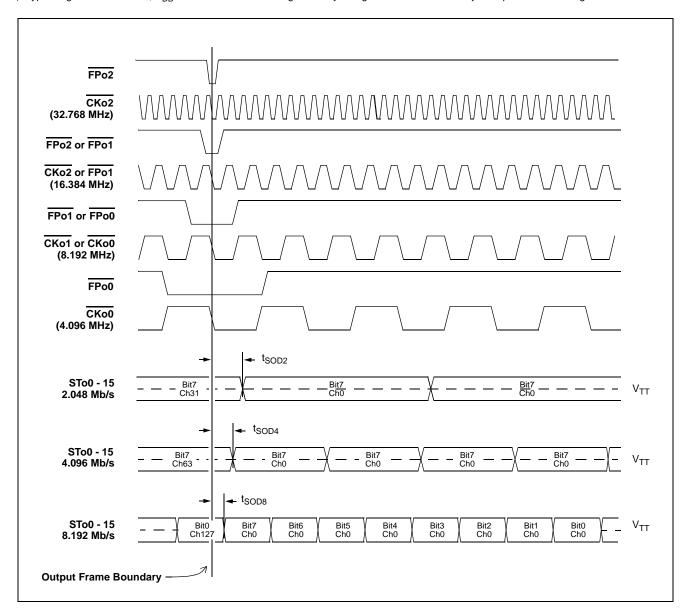

By default, the output frame boundary is defined by the falling edge of the CKo0, CKo1 or CKo2 output clock while the FPo0, FPo1 or FPo2 output frame pulse goes low respectively. When the output data rates are 2.048 Mb/s, 4.096 Mb/s and 8.192 Mb/s, there are 32, 64 or 128 output channels per every ST-BUS frame respectively. Figure 14 describes the details.

Figure 14 - ST-BUS Output Timing for Various Output Data Rates

#### 2.3 Serial Data Input Delay and Serial Data Output Offset

Various registers are provided to adjust the input and output delays for every input and every output data stream. The input and output channel delay can vary from 0 to 31, 0 to 63 and 0 to 127 channel(s) for the 2.048 Mb/s, 4.096 Mb/s and 8.192 Mb/s modes respectively.

The input and output bit delay can vary from 0 to 7 bits. The fractional input bit delay can vary from 1/4, 1/2, 3/4 to 4/4 bit. The fractional output bit advancement can vary from 0, 1/4, 1/2 to 3/4 bit.

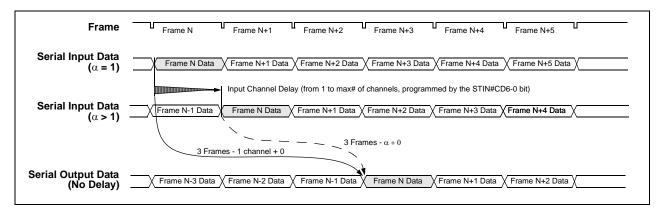

#### 2.3.1 Input Channel Delay Programming

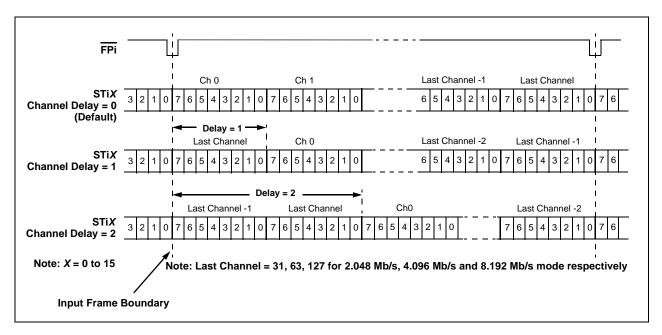

This feature allows each input stream to have a different input frame boundary with respect to the input frame boundary defined by the FPi and CKi. By default, all input streams have channel delay of zero such that Ch0 is the first channel that appears after the input frame boundary (see Figure 15).

The input channel delay programming is enabled by setting Bit 3 to 9 in the Stream Input Delay Register (SIDR). The input channel delay can vary from 0 to 31, 0 to 63 and 0 to 127 for the 2.048 Mb/s, 4.096 Mb/s and 8.192 Mb/s modes respectively.

Figure 15 - Input Channel Delay Timing Diagram

#### 2.3.2 Input Bit Delay Programming

In addition to the input channel delay programming, the input bit delay programming feature provides users with more flexibility when designing the switch matrices at high speed, in which the delay lines are easily created on PCM highways which are connected to the switch matrix cards.

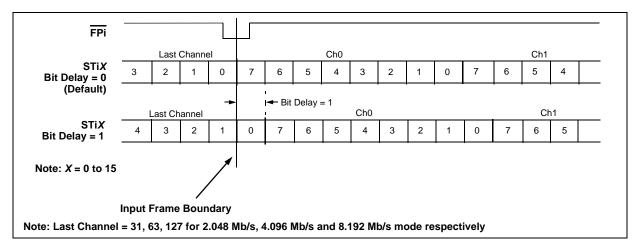

By default, all input streams have zero bit delay such that Bit 7 is the first bit that appears after the input frame boundary, see Figure 16. The input delay is enabled by Bit 0 to 2 in the Stream Input Delay Registers (SIDR). The input bit delay can vary from 0 to 7 bits.

#### 2.3.3 Fractional Input Bit Delay Programming

In addition to the input bit delay feature, the device allows users to change the sampling point of the input bit. By default, the sampling point is at 3/4 bit. Users can change the sampling point to 1/4, 1/2, 3/4 or 4/4 bit position by programming Bit 3 and 4 of the Stream Input Control Registers (SICR).

Figure 16 - Input Bit Delay Timing Diagram

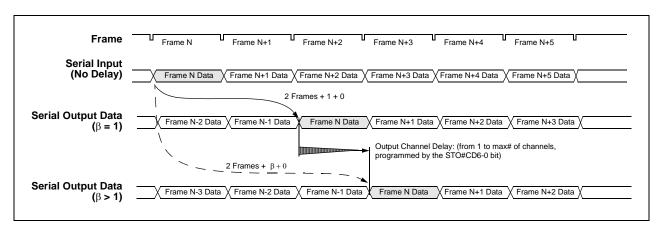

#### 2.3.4 Output Channel Delay Programming

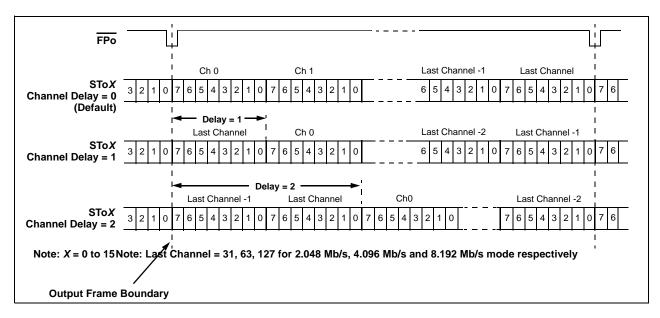

This feature allows each output stream to have a different output frame boundary with respect to the output frame boundary defined by the output frame pulse (FPo0, FPo1 and FPo2) and the output clock (CKo0, CKo1 or CKo2). By default, all output streams have zero channel delay such that Ch 0 is the first channel that appears after the output frame boundary as shown in Figure 17. Different output channel delay can be set by programming Bit 5 to 11 in the Stream Output Offset Registers (SOOR). The output channel delay can vary from 0 to 31, 0 to 63 and 0 to 127 for the 2.048 Mb/s, 4.096 Mb/s and 8.192 Mb/s modes respectively.

Figure 17 - Output Channel Delay Timing Diagram

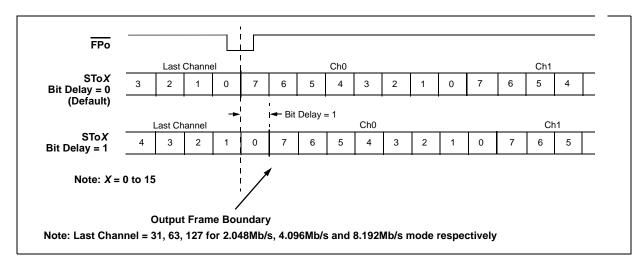

#### 2.3.5 Output Bit Delay Programming

This feature is used to delay the output data bit of individual output streams with respect to the output frame boundary. Each output stream can have its own bit delay value.

By default, all output streams have zero bit delay such that Bit 7 is the first bit that appears after the output frame boundary (see Figure 18 on page 25). Different output bit delay can be set by programming Bit 2 to 4 in the Stream Output Offset Registers. The output bit delay can vary from 0 to 7 bits.

Figure 18 - Output Bit Delay Timing Diagram

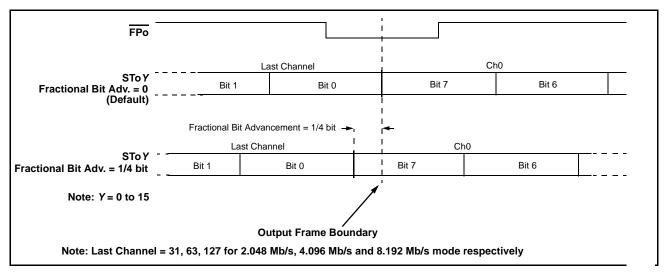

#### 2.3.6 Fractional Output Bit Advancement Programming

In addition to the output bit delay, the device is also capable of performing fractional output bit advancement. This feature offers a better resolution for the output bit delay adjustment. The fractional output bit advancement is useful in compensating for various parasitic loadings on the serial data output pins.

By default, all output streams have zero fractional bit advancement such that Bit 7 is the first bit that appears after the output frame boundary as shown in Figure 19. The fractional output bit advancement is enabled by Bit 0 to 1 in the Stream Output Offset Registers. The fractional bit advancement can vary from 0, 1/4, 1/2 or 3/4 bit.

Figure 19 - Fractional Output Bit Advancement Timing Diagram

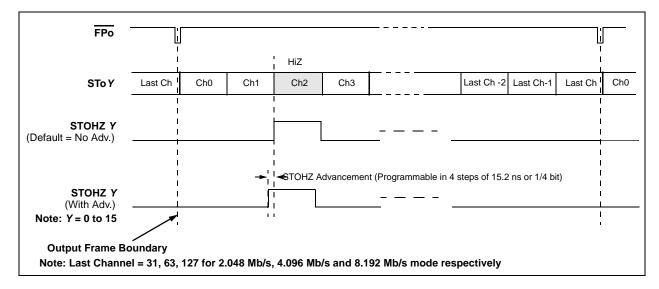

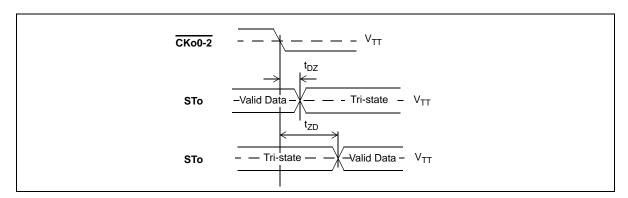

#### 2.3.7 External High Impedance Control, STOHZ 0 to 15

The STOHZ 0 to 15 outputs are provided to control the external tristate ST-BUS drivers for per-channel high impedance operations. The STOHZ outputs are sent out in 32, 64 or 128 timeslots corresponding to the output channels for 2.048 Mb/s, 4.096 Mb/s and 8.192 Mb/s output streams respectively. Each control timeslot lasts for one channel time.

When the ODE pin is high, the STOHZ 0 - 15 are enabled. When the ODE pin or the RESET pin is low, the STOHZ 0 - 15 are driven high. STOHZ outputs are also driven high if their corresponding ST-BUS outputs are not in use.

Figure 20 gives an example when channel 2 of a given ST-BUS output is programmed in the high impedance state, the corresponding STOHZ pin drives high for one channel time at the channel 2 timeslot.

By default, the output timing of the STOHZ signals follow the same timing as their corresponding STo signals including any user-programmed output channel and bit delay and fractional bit advancement. In addition, the device allows users to advance the STOHZ signals from their default positions to a maximum of four 15.2 ns steps (or four 1/4 bit steps) using Bit 3 to 5 of the Stream Output Control Register (SOCR). Bit 6 in the Stream Output Control Register selects the step resolution as 15.2 ns or 1/4 data bit. The additional advancement feature allows the STOHZ signals to better match the high impedance timing required by the external ST-BUS drivers.

Figure 20 - Example: External High Impedance Control Timing

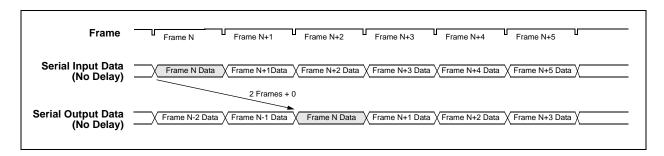

#### 2.4 Data Delay Through The Switching Paths

To maintain the channel integrity in the constant delay mode, the usage of the input channel delay and output channel delay modes affect the data delay through various switching paths due to additional data buffers. The usage of these data buffers is enabled by the input and output channel delay bits (STIN#CD6-0 and STO#CD6-0) in the Stream Input Delay and Stream Output Offset Registers. However, the input and output bit delay or the input and output fractional bit offset have no impact on the overall data throughput delay.

In the following paragraphs, the data throughput delay (T) is expressed as a function of ST-BUS frames, input channel number (m), output channel number (n), input channel delay ( $\alpha$ ) and output channel delay ( $\beta$ ). Table 5 describes the variable range for input streams and Table 6 describes the variable range for output streams. Table 7 summarizes the data throughput delay under various input channel and output channel delay conditions.

| Input Stream<br>Data Rate | Possible Inpu |          |

|---------------------------|---------------|----------|

| 2 Mb/s                    | 0 to 31       | 1 to 31  |

| 4 Mb/s                    | 0 to 63       | 1 to 63  |

| 8 Mb/s                    | 0 to 127      | 1 to 127 |

**Table 5 - Variable Range for Input Streams**

| Output Stream<br>Data Rate | Output Channel<br>Number (n) | Possible Output channel delay (β) |

|----------------------------|------------------------------|-----------------------------------|

| 2 Mb/s                     | 0 to 31                      | 1 to 31                           |

| 4 Mb/s                     | 0 to 63                      | 1 to 63                           |

| 8 Mb/s                     | 0 to 127                     | 1 to 127                          |

**Table 6 - Variable Range for Output Streams**

| Input Channel Delay OFF Output Channel Delay OFF Output Channel Delay OFF |                                 | Input Channel Delay OFF<br>Output Channel Delay ON | Input Channel Delay ON<br>Output Channel Delay ON |  |

|---------------------------------------------------------------------------|---------------------------------|----------------------------------------------------|---------------------------------------------------|--|

| T = 2 frames + (n-m)                                                      | T = 3 frames - $\alpha$ + (n-m) | T = 2 frames + $\beta$ + (n-m)                     | T= 3 frames - $\alpha$ + $\beta$ + (n-m)          |  |

Table 7 - Data Throughput Delay

By default, when the input channel delay and output channel delay are set to zero, the data throughput delay (T) is: T = 2 frames + (m-n). Figure 21 shows the throughput delay when the input Ch0 is switched to the output Ch0.

Figure 21 - Data Throughput Delay when input and output channel delay are disabled for Input Ch0 switched to Output Ch0

When the input channel delay is enabled and the output channel delay is disabled, the data throughput delay is: T = 3 frames -  $\alpha + (m-n)$ . Figure 22 shows the data throughput delay when the input Ch0 is switched to the output Ch0.

Figure 22 - Data Throughput Delay when input channel delay is enabled and output channel delay is disabled for Input Ch0 switched to Output Ch0

When the input channel delay is disabled and the output channel delay is enabled, the throughput delay is: T = 2 frames +  $\beta$  + (m-n). Figure 23 shows the data throughput delay when the input Ch0 is switched to the output Ch0.

Figure 23 - Data Throughput Delay when input channel delay is disabled and output channel delay is enabled for Input Ch0 switch to Output Ch0

ZL50012 Data Sheet

When the input channel delay and the output channel delay are enabled, the data throughput delay is: **T = 3 frames** -  $\alpha$  +  $\beta$  + (m-n). Figure 24 shows the data throughput delay when the input Ch0 is switched to the output Ch0.

Figure 24 - Data Throughput Delay when input and output channel delay are enabled for Input Ch0 switched to Output Ch0

#### 2.5 Connection Memory Description

The connection memory is 12-bit wide. There are 512 memory locations to support the ST-BUS serial outputs STo0-15. The address of each connection memory location corresponds to an output destination stream number and an output channel address. See Table 28 on page 52 for the connection memory address map.

When Bit 0 of the connection memory is **low**, Bit 1 to 7 define the source (input) channel address and Bit 8 to 11 define the source (input) stream address. Once the source stream and channel addresses are programmed by the microprocessor, the contents of the data memory at the selected address are switched to the mapped output stream and channel. See Table 29 on page 53 for details on the memory bit assignment when Bit 0 of the connection memory is low.

When Bit 0 of the connection memory is **high**, Bit 1 and 2 define the per-channel control modes of the output streams, the per-channel high impedance output control, the per-channel message and the per-channel BER test modes. In the message mode, the 8-bit message data located in Bit 3 to 10 of the connection memory will be transferred directly to the mapped output stream. See Table 30 on page 53 for details on the memory bit assignment when Bit 0 of the connection memory is high.

#### 2.5.1 Connection Memory Block Programming

This feature allows fast initialization of the entire connection memory after power up. When block programming mode is enabled, the content of Bit 1 to 3 in the Internal Mode Selection (IMS) Register will be loaded into Bit 0 to 2 of all the 512 connection memory locations. The other bit positions of the connection memory will be loaded with zeros.

#### Memory block programming procedure:

(Assumption: The MBPE and MBPS bits are both low at the start of the procedure)

- Program Bit 1 to 3 (BPD0 to BPD2) in the IMS (Internal Mode Selection) register.

- Set the Memory Block Programming Enable (MBPE) bit in the Control Register to high to enable the block programming mode.

- Set the Memory Block Programming Start (MBPS) bit to high in the IMS Register to start the block programming. The BPD0 to BPD2 bits will be loaded into Bit 0 to 2 of the connection memory. The other bit positions of the connection memory will be loaded with zeros. The memory content after block programming is shown in Table 8.

- It takes 50µs for the connection memory to be loaded with the bit pattern defined by the BPD0 to BPD2 bits.

- After loading the bit pattern to the entire connection memory, the device will reset the MBPS bit to low, indicating that the process has finished.

- Upon completion of the block programming, set the MBPE bit from high to low to disable the block programming mode.

**Note**: Once the block programming is started, it can be terminated at any time prior to completion by setting the MBPS bit or the MBPE bit to low. If the MBPE bit is used to terminate the block programming before completion, users have to set the MBPS bit from high to low before enabling other device operation.

| 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|----|----|---|---|---|---|---|---|---|------|------|------|

| 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | BPD2 | BPD1 | BPD0 |

Table 8 - Connection Memory in Block Programming Mode

ZL50012 Data Sheet

#### 2.6 Bit Error Rate (BER) Test

The ZL50012 has one on-chip BER transmitter and one BER receiver. The transmitter can transmit onto a single STo output stream only. The transmitter provides a BER sequence ( $2^{15}$ -1 Pseudo Random Code) which can start from any channel in the frame and lasts from one channel up to one frame time (125  $\mu$ s). The transmitter output channel(s) are specified by programming the connection memory location(s) corresponding to the channel(s) of the selected output stream: Bit 0 to 2 of the connection memory location(s) should be programmed to the BER test mode (see Table 30 on page 53).

Multiple connection memory locations can be programmed for BER test such that the BER patterns can be transmitted for several output channels which are consecutive. If the transmitting output channels are not consecutive, the BER receiver will not compare the bit patterns correctly.

The number of output channels which the BER transmitter occupies also has to be the same as the number of channels defined in the BER Length Register. The BER Length Register defines how many BER channels to be monitored by the BER receiver.

Registers used for setting up the BER test are as follows:

- Control Register (CR) The CBER bit is used to clear the bit error counter and the BER Count Register (BCR). The SBER bit is used to start or stop the BER transmitter and BER receiver.

- BER Start Receiving Register (BSRR) Defines the input stream and channel from where the BER sequence will start to be compared.

- BER Length Register (BLR) Defines how many channels the sequence will last.

- BER Count Register (BCR) Contains the number of counted errors. When the error count reaches Hex

FFFF, the bit error counter will stop so that it will not overflow. Consequently the BER Count Register will

also stop at FFFF. The CBER bit in the Control Register is used to reset the bit error counter and the BER

Count Register.

As described above, the SBER bit in the control register controls the BER transmitter and receiver. To carry out the BER test, users should set the SBER bit to zero to disable the BER transmitter during the programming of the connection memory for the BER test. When the BER transmitter is disabled, the transmitter output is all ones. Hence any output channel whose connection memory has been programmed to BER test mode will also output all ones. Upon the completion of programming the connection memory for the BER test, set the SBER bit to one to start the BER transmitter and receiver for the BER testing. They must be allowed to run for several frames (2 frames plus the network delay between STo and STi) before the BER receiver can correctly identify errors in the pattern. Thus after this time the bit error counter should be reset by using the CBER bit in the Control Register - set CBER to one then back to zero. From now on, the count will be the actual number of errors which occurred during the test. The count will stop at FFFF and the counter will not increment even if more errors occurred.

#### 2.7 Quadrant frame programming

By programming the input stream control registers (SICR0 to 15), users can divide one frame of input data into four quadrant frames and can force the Least Significant Bit (LSB, bit 0 in Figure 7 on page 18), of every input channel in these quadrants into "1" for the bit robbed signaling purpose. The four quadrant frames are defined as shown in Table 9.

| Data Rate  | Quadrant 0 Quadrant 1 |             | Quadrant 2  | Quadrant 3   |  |

|------------|-----------------------|-------------|-------------|--------------|--|

| 2.048 Mb/s | Ch 0 to 7             | Ch 8 to 15  | Ch 16 to 23 | Ch 24 to 31  |  |

| 4.096 Mb/s | Ch 0 to 15            | Ch 16 to 31 | Ch 32 to 47 | Ch 48 to 63  |  |

| 8.192 Mb/s | Ch 0 to 31            | Ch 32 to 63 | Ch 64 to 95 | Ch 96 to 127 |  |

**Table 9 - Definition of the Four Quadrant Frames**

When a quadrant frame enable bit (STIN#QEN0, STIN#QEN1, STIN#QEN2 or STIN#QEN3) is set to high, the LSB of every input channels in the quadrant is forced to "1". See Table 10 to Table 13 for details:

| STIN#QEN0 Action |                                                     |

|------------------|-----------------------------------------------------|

| 1                | Replace LSB of every channel in Quadrant 0 with "1" |

| 0                | No bit replacement occurs in Quadrant 0             |

Table 10 - Quadrant Frame 0 LSB Replacement

| STIN#QEN1 | Action                                              |

|-----------|-----------------------------------------------------|

| 1         | Replace LSB of every channel in Quadrant 1 with "1" |

| 0         | No bit replacement occurs in Quadrant 1             |

**Table 11 - Quadrant Frame 1 LSB Replacement**

| STIN#QEN2 | Action                                              |  |

|-----------|-----------------------------------------------------|--|

| 1         | Replace LSB of every channel in Quadrant 2 with "1" |  |

| 0         | No bit replacement occurs in Quadrant 2             |  |

Table 12 - Quadrant Frame 2 LSB Replacement

| STIN#QEN3 | Action                                              |

|-----------|-----------------------------------------------------|

| 1         | Replace LSB of every channel in Quadrant 3 with "1" |

| 0         | No bit replacement occurs in Quadrant 3             |

Table 13 - Quadrant Frame 3 LSB Replacement

#### 2.8 Microprocessor Port

The device supports the non-multiplexed microprocessor. The microprocessor port consists of a 16-bit parallel data bus (D0 to 15), a 12-bit address bus (A0 to 11) and four control signals (CS, DS, R/W and DTA). The parallel microprocessor port provides fast access to the internal registers, the connection and the data memories.

The connection memory locations can be read or written via the 16-bit microprocessor port. On the other hand, the data memory locations can only be read (but not written) from the microprocessor port.

For the connection memory write operation, D0 to 11 of the data bus will be used and D12 to 15 are ignored (D12 to 15 should be driven low). For the connection memory read operation, D0 to D11 will be used and D12 to D15 will output zeros. For the data memory read operation, D0 to D7 will be used and D8 to D15 will output zeros.

See Table 28 on page 52 for the address mapping of the data memory. Refer to Figure 36 on page 65 for the microprocessor port timing.

#### 3.0 Device Reset and Initialization

The RESET pin is used to reset the device. When the pin is low, it synchronously puts the device in its reset state. It disables the ST00 - 15 outputs, drives the ST0HZ 0 - 15 outputs to high, clears the device registers and the internal counters.

Upon power up, the device should be initialized as follows:

- Set ODE pin to low to disable the STo0-15 output and to drive the STOHZ 0-15 to high.

- Set the TRST pin to low to disable the JTAG TAP controller.

- Reset the device by pulsing the RESET pin to low for longer than 1ms.

- After releasing the RESET pin from low to high, wait for 600 μs for the APLL module to be stabilized before starting the first microprocessor port access cycle.

- Program the register to define the frequency of the CKi input.

- Wait for 600 μs for the APLL module to be stabilized before starting the next microprocessor port access cycle.

- Use the memory block programming mode to initialize the connection memory.

- Release the ODE pin to high after the connection memory is programmed such that bus contention will not occur at the serial stream outputs STo0-15.

#### 4.0 JTAG Support

The ZL50012 JTAG interface conforms to the Boundary-Scan IEEE1149.1 standard. The operation of the boundary-scan circuitry is controlled by an external Test Access Port (TAP) Controller.

#### 4.1 Test Access Port (TAP)

The Test Access Port (TAP) accesses the ZL50012 test functions. It consists of three input pins and one output pin as follows:

- Test Clock Input (TCK) TCK provides the clock for the test logic. The TCK does not interfere with any onchip clock and thus remains independent in the functional mode. The TCK permits shifting of test data into or out of the Boundary-Scan register cells concurrently with the operation of the device and without interfering with the on-chip logic.

- **Test Mode Select Input (TMS)** The TAP Controller uses the logic signals received at the TMS input to control test operations. The TMS signals are sampled at the rising edge of the TCK pulse. This pin is internally pulled to Vdd when it is not driven from an external source.

ZL50012 Data Sheet

- Test Data Input (TDi) Serial input data applied to this port is fed either into the instruction register or into a

test data register, depending on the sequence previously applied to the TMS input. Both registers are

described in a subsequent section. The received input data is sampled at the rising edge of TCK pulses.

This pin is internally pulled to Vdd when it is not driven from an external source.

- Test Data Output (TDo) Depending on the sequence previously applied to the TMS input, the contents of either the instruction register or data register are serially shifted out towards the TDO. The data out of the TDO is clocked on the falling edge of the TCK pulses. When no data is shifted through the boundary scan cells, the TDO driver is set to a high impedance state.

- Test Reset (TRST) Resets the JTAG scan structure. This pin is internally pulled to Vdd when it is not driven from an external source.

#### 4.2 Instruction Register

The ZL50012 uses the public instructions defined in the IEEE 1149.1 standard. The JTAG Interface contains a four-bit instruction register. Instructions are serially loaded into the instruction register from the TDI when the TAP Controller is in its shifted-IR state. These instructions are subsequently decoded to achieve two basic functions: to select the test data register that may operate while the instruction is current and to define the serial test data register path that is used to shift data between TDI and TDO during data register scanning.

#### 4.3 Test Data Register

As specified in IEEE 1149.1, the ZL50012 JTAG Interface contains three test data registers:

- The Boundary-Scan Register The Boundary-Scan register consists of a series of Boundary-Scan cells arranged to form a scan path around the boundary of the ZL50012 core logic.

- The Bypass Register The Bypass register is a single stage shift register that provides a one-bit path from TDI to its TDO.

- The Device Identification Register The JTAG device ID for the ZL50012 is 0C35C14B<sub>H</sub>.

Version<31:28>: 0000

Part No. <27:12>: 1100 0011 0101 1100

Manufacturer ID<11:1>: 0001 0100 101

LSB<0>: 1

#### 4.4 BSDL

A BSDL (Boundary Scan Description Language) file is available from Zarlink Semiconductor to aid in the use of the IEEE 1149 test interface.

# 5.0 Register Address Mapping

| External<br>Address<br>A11 - A0 | CPU<br>Access | Register                                |

|---------------------------------|---------------|-----------------------------------------|

| 000 <sub>H</sub>                | R/W           | Control Register, CR                    |

| 001 <sub>H</sub>                | R/W           | Internal Mode Selection, IMS            |

| 010 <sub>H</sub>                | R/W           | BER Start Receive Register, BSRR        |

| 011 <sub>H</sub>                | R/W           | BER Length Register, BLR                |

| 012 <sub>H</sub>                | Read Only     | BER Count Register, BCR                 |

| 030 <sub>H</sub>                | Read Only     | Reserved                                |